# IP CORE PROTECTION AND DETECTIVE CONTROL OF DATA-INTENSIVE HARDWARE IPS AGAINST PIRACY

Ph.D. Thesis

# By RAHUL CHAURASIA

# DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE MAY 2023

# IP CORE PROTECTION AND DETECTIVE CONTROL OF DATA-INTENSIVE HARDWARE IPS AGAINST PIRACY

### **A THESIS**

Submitted in partial fulfillment of the requirements for the award of the degree

OJ DOCTOR OF PHILOSOPHY

by RAHUL CHAURASIA

# DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE MAY 2023

# INDIAN INSTITUTE OF TECHNOLOGY INDORE

## CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled IP CORE PROTECTION AND DETECTIVE CONTROL OF DATA-INTENSIVE HARDWARE IPS AGAINST PIRACY in the partial fulfillment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY and submitted in the DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING, INDIAN INSTITUTE OF TECHNOLOGY INDORE, is an authentic record of my own work carried out during the time period from DECEMBER, 2020 to MAY 2023 under the supervision of Dr. ANIRBAN SENGUPTA, Associate Professor, Indian Institute of Technology, Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

| Signature of the student with date |

|------------------------------------|

| (RAHUL CHAURASIA)                  |

This is to certify that the above statement made by the candidate is correct to the best of my/our knowledge.

Signature of Thesis Supervisor with date (ANIRBAN SENGUPTA)

RAHUL CHAURASIA has successfully given his/her Ph.D. Oral Examination held on

| Signature of Chairperson (OEB) Date: | Signature of External Examiner Date:  | Signature(s) of Thesis Supervisor(s) Date: |

|--------------------------------------|---------------------------------------|--------------------------------------------|

| Signature of PSPC Member #1 Date:    | Signature of PSPC Member #2<br>Date:  | Signature of PSPC Member #3 Date:          |

| Signature of Convener, DPGC Date:    | Signature of Head of Discipline Date: |                                            |

### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to thank a number of persons who in one or the other way contributed by making this time as learnable and enjoyable, as possible. First and foremost, I wish to express my sincere gratitude to my supervisor **Dr. Anirban Sengupta** for providing me the opportunity to do work under his supervision. I wish to thank him for his persistence and faith in me. Without his relentless effort and guidance I would have not been to understand the importance of research and the sacrifice it requires to reach a certain level. Under his supervision, I transformed into a person with more values and learnt the importance of work ethics, scientific temperament and intellectual firepower.

I also owe a mention to **Dr. Abhishek Srivastava** and **Dr. Sampak Samanta** for their valuable feedbacks on my research work throughout these years.

I am also grateful to **Dr. Somnath Dey**, Head of the Department of Computer Science & Engineering, for extending all necessary support to me. My sincere acknowledgement and respect to **Prof. Suhas Joshi**, Director, Indian Institute of Technology Indore, for providing me the opportunity to explore my research capabilities at the Indian Institute of Technology Indore.

I wish to thank all the faculty members, my lab mate Dr. Mahendra Rathor, Aditya Anshul and friends for their continuous support. I appreciate the support of Mr. Utpal (Baba), Mrs. Purnima (Maa) and Mrs. Neha Ghosh.

Further, I wish to express my deepest gratitude to my parents, for their strong belief in me and for their continuous support all the way. I also wish to express my gratitude to my caring sisters, Priyanka and Deeksha and my brother Rajesh for being the driving force of my career and for her moral and emotional support throughout the PhD work. I am thankful to all for being with me every single moment to keep me motivated to work for the past years.

At last, I wish to thank IIT Indore and UGC to help financially and providing me an opportunity to present my research at international platforms.

Rahul Chaurasia

# DEDICATED TO MY FATHER LATE SHRI VIJAY KUMAR CHAURASIA (V.K.C)

## **ABSTRACT**

Hardware IP core based design paradigm has become popular, for its usage in several consumer electronics and computing systems. This is because the usage of hardware IP cores enables higher performance and efficacy by accelerating the underlying process of the respective application. Further, due to their data intensive nature and factors such as time to market pressure, process turnaround time and design complexity are some of the major reasons that have enforced or encouraged reusable IP core-based system on chip (SoC) designs. This scenario leads to involvement of third-party IP vendors to match demand and supply ratio or to accelerate the design process, thereby making it susceptible to different hardware security threats. An adversary in the untrusted offshore design house may pirate the IP core(s) for their own benefits or to satisfy malicious intensions, causing safety and integrity hazards to end consumer.

The digital signal processing (DSP), multimedia and machine learning applications are thriving in the modern consumer electronics (CE) market. These IP cores are used for facilitating several crucial applications in the domain of health care, robotics and artificial intelligence (AI) etc. Hence, they have become an important and integral part of modern electronic/automated devices. Therefore, the current generations of system on chip (SoC) designers amalgamate reusable IP cores imported from multiple vendors/manufacturers. These IP cores are mass-produced, tested and verified by various companies and this IP supply chain is distributed worldwide. Therefore, due to involvement of multi-party vendors, their security concerns cannot be undervalued. Hence, an IP core designer needs to employ robust and seamless security measures against security threats to ensure trust in hardware IP. For DSP, multimedia and machine learning based applications which are highly complex or data intensive in nature, their realization as reusable hardware IP cores is crucial. Further, to ensure their security against hardware threats, a high-level synthesis (HLS) framework is conducive for integrating security mechanisms. HLS offers lesser design complexity and flexibility to integrate the security mechanisms. Therefore, enabling an IP designer to achieve robust security while incurring negligible or lower design cost

overhead concurrently. Towards the security of IP cores, this thesis contributes the following: (a) contact-less palmprint biometric for securing DSP coprocessors used in CE systems against IP piracy, (b) double line of defense approach for securing DSP IP cores using structural obfuscation and chromosomal DNA impression, (c) designing secured reusable convolutional IP core in convolutional neural network (CNN) using facial biometric based hardware security approach, (d) Retinal biometric based secured JPEG-codec hardware IP core design for CE systems using HLS and (e) exploration of security-cost tradeoff for signature driven security algorithms for optimal architecture of data-intensive hardware IPs.

## **LIST OF PUBLICATIONS (21)**

### PEER-REVIEWED JOURNALS (8):

- A. Sengupta, R. Chaurasia and T. Reddy, "Contact-Less Palmprint Biometric for Securing DSP Coprocessors Used in CE Systems," *IEEE Trans. Consum. Electron.*, vol. 67, no. 3, pp. 202-213, Aug. 2021, doi: 10.1109/TCE.2021.3105113. (Impact Factor: 4.414)

- 2. A. Sengupta and R. Chaurasia, "Secured Convolutional Layer IP Core in Convolutional Neural Network Using Facial Biometric," *IEEE Trans. Consum. Electron.*, vol. 68, no. 3, pp. 291-306, Aug. 2022, doi: 10.1109/TCE.2022.3190069. (Impact Factor: 4.414)

- 3. R. Chaurasia and A. Sengupta, "Retinal Biometric for Securing JPEG-Codec Hardware IP core for CE systems," *IEEE Trans. Consum. Electron.*, Accepted, April, 2023, (Impact Factor: 4.414)

- A. Sengupta, R. Chaurasia and A. Anshul, "Robust Security of Hardware Accelerators using Protein Molecular Biometric Signature and Facial Biometric Encryption Key," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, 2023, doi: 10.1109/TVLSI.2023.3265559. (Impact Factor: 2.775)

- M. Rathor, A. Sengupta, R. Chaurasia and A. Anshul "Exploring Handwritten Signature Image Features for Hardware Security", *IEEE Trans. Dependable Secure* Comput. (TDSC), 2022, doi: 10.1109/TDSC.2022.3218506. (Impact Factor: 6.791)

- A. Sengupta and R. Chaurasia, "Securing IP Cores for DSP Applications Using Structural Obfuscation and Chromosomal DNA Impression," *IEEE Access*, vol. 10, pp. 50903-50913, 2022, doi: 10.1109/ACCESS.2022.3174349. (Impact Factor: 3.476).

- R. Chaurasia, A. Anshul, A. Sengupta and S. Gupta, "Palmprint Biometric Versus Encrypted Hash Based Digital Signature for Securing DSP Cores Used in CE Systems," *IEEE Consum. Electron. Mag. (CEM)*, vol. 11, no. 5, pp. 73-80, 1 Sept. 2022, doi: 10.1109/MCE.2022.3153276. (Impact Factor: 4.135)

- 8. M. Rathor, A. Anshul, K. Bharath, R. Chaurasia and A. Sengupta "Quadruple Phase Watermarking during High Level Synthesis for Securing Reusable Hardware IP Cores", "*Computers and Electrical Engineering*", vol. 105, 2023, doi.org/10.1016/j.compeleceng.2022.108476. (Impact Factor: 4.152)

#### BOOK CHAPTERS (8):

- 9. **R.** Chaurasia, A. Sengupta and P. Pradeeprao "Secured Integrated Circuit (IC/IP) Design Flow", *CRC Book "Nanoelectronics for Next-generation Integrated Circuits*", 2022, eBook ISBN9781003155751.

- A. Sengupta and R. Chaurasia "Hardware IP Cores for Image Processing Functions", IOP Book "Advances in Image and Data Processing using VLSI Design", 2022, pp. 7.1 - 7.14, doi: 10.1088/978-0-7503-3919-3ch7.

- 11. A. Sengupta and R. Chaurasia "Integrated Defense using Structural obfuscation and Encrypted DNA based Biometric for Hardware Security," *IET Book "Physical Biometrics for Hardware Security of DSP and Machine Learning Coprocessors*", 2022, Accepted.

- A. Anshul, R. Chaurasia and A. Sengupta "Securing Hardware Coprocessors against Piracy using Biometrics for Secured IoT systems," *IET Book "Artificial Intelligence for Biometrics and Cybersecurity*", 2022, Accepted.

- A. Sengupta and R. Chaurasia "Facial Signature based Biometrics for Hardware Security and IP Core protection," *IET Book "Physical Biometrics for Hardware Security of DSP and Machine Learning Coprocessors"*, 2022, Accepted.

- 14. A. Sengupta and R. Chaurasia "Secured Convolutional Layer Hardware Coprocessor in Convolutional Neural Network (CNN) using Facial Biometric," IET Book "Physical Biometrics for Hardware Security of DSP and Machine Learning Coprocessors", 2022, Accepted.

- 15. A. Sengupta and R. Chaurasia "Handling Symmetrical IP Core Protection and IP Protection (IPP) of Trojan Secured Designs in HLS using Physical Biometrics," IET Book "Physical Biometrics for Hardware Security of DSP and Machine Learning Coprocessors", 2022, Accepted.

- 16. A. Sengupta and R. Chaurasia "Methodology for Exploration of Security-Design Cost Tradeoff for Signature-based Security Algorithms," IET Book "Physical Biometrics for Hardware Security of DSP and Machine Learning Coprocessors", 2022, Accepted.

#### PEER- REVIEWED CONFERENCE PUBLICATIONS (5):

- 17. **R.** Chaurasia and A. Sengupta, "Securing Reusable Hardware IP cores using Palmprint Biometric," *2021 IEEE International Symposium on Smart Electronic Systems (iSES)*, 2021, pp. 410-413, doi: 10.1109/iSES52644.2021.00099.

- R. Chaurasia and A. Sengupta, "Crypto-Genome Signature for Securing Hardware Accelerators," 2022 IEEE 19th India Council International Conference (INDICON), India, 2022, pp. 1-6, doi: 10.1109/INDICON56171.2022.10039955.

- R. Chaurasia and A. Sengupta, "Protecting Trojan Secured DSP cores against IP piracy using Facial Biometrics," 2022 IEEE 19th India Council International Conference (INDICON), India, 2022, pp. 1-6, doi: 10.1109/INDICON56171.2022.10039864.

- R. Chaurasia and A. Sengupta, "Security Vs Design Cost of Signature Driven Security Methodologies for Reusable Hardware IP Core," 2022 IEEE International Symposium on Smart Electronic Systems (iSES), India, 2022, pp. 283-288, doi: 10.1109/iSES54909.2022.00064.

- R. Chaurasia and A. Sengupta, "Symmetrical Protection of Ownership Right's for IP Buyer and IP Vendor using Facial Biometric Pairing," 2022 IEEE International Symposium on Smart Electronic Systems (iSES), India, 2022, pp. 272-277, doi: 10.1109/iSES54909.2022.00062.

# **TABLE OF CONTENTS**

|    | LIST O     | F PUBLICATIONS<br>F FIGURES<br>F TABLES<br>NCLATURE                                                           | VI<br>VII<br>XII<br>XVI<br>XIX<br>XXI |

|----|------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 1. | Chapter    | 1                                                                                                             | 1                                     |

|    | Introduc   | etion                                                                                                         |                                       |

|    | 1.1        | Different design abstraction levels and corresponding form of hardware IP core                                | 3                                     |

|    | 1.2        | DSP, machine learning and multimedia-based applications and their algorithmic representation                  | 3                                     |

|    | 1.3        | Threats to reusable data intensive hardware IP cores                                                          | 4                                     |

|    | 1.4        | Background on high level synthesis and its importance in designing secured and low-cost reusable hardware IPs | 7                                     |

|    | 1.5        | Organization of thesis                                                                                        | 10                                    |

| 2. | Chapter    | 2                                                                                                             | 11                                    |

|    | State of   | the art                                                                                                       |                                       |

|    | 2.1        | State of the art on handling IP piracy and fraudulent claim of ownership threat                               | 11                                    |

|    | 2.2<br>2.3 | State of the art on handling reverse engineering threat<br>State of the art on handling Symmetrical IP core   | 15                                    |

|    | 2.4        | protection Objective of the thesis                                                                            | 17                                    |

|    | 2.5        | Summary of the contributions                                                                                  | 18                                    |

| 3. | Chapter    | 3                                                                                                             | 21                                    |

|    |            | -less palmprint biometric for securing DSP coprocessors<br>CE systems against IP piracy                       |                                       |

|    | 3.1        | Problem formulation                                                                                           | 22                                    |

|    | 3.2        | Biometric digital template generation based on captured palmprint of an IP vendor                             | 22                                    |

|    | 3.3        | Demonstration on generating palmprint embedded secured RT level design for FIR filter using HLS               | 30                                    |

|    | 3.4        | Metric for evaluating impact of proposed palmprint                                                            | 40                                    |

|    | 3.5        | biometric technique on design cost<br>Summary                                                                 | 41                                    |

| 4. | Chapter    | 4                                                                                                                           | 42       |

|----|------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

|    |            | line of defense approach for securing DSP IP cores using all obfuscation and chromosomal DNA impression                     |          |

|    | 4.1<br>4.2 | Problem formulation Security mechanism with double line of defense for securing IP core design                              | 43<br>43 |

|    | 4.3        | Demonstration on generating secured 4-point DFT design                                                                      | 50       |

|    | 4.4        | Summary                                                                                                                     | 51       |

| 5. | Chapter    | 5                                                                                                                           | 52       |

|    | _          | ng secured reusable convolutional IP core in CNN using ometric based hardware security approach                             |          |

|    | 5.1        | Problem formulation                                                                                                         | 52       |

|    | 5.2        | HLS flow for designing secured convolutional IP core                                                                        | 52       |

|    | 5.3        | Demonstration on generating secured convolutional IP datapath design using facial biometric                                 | 60       |

|    | 5.4        | Demonstration on hardware based convolutional process using proposed convolutional IP                                       |          |

|    | 5.5        | Summary                                                                                                                     | 66       |

| 6. | Chapter    | 6                                                                                                                           | 67       |

|    |            | piometric based secured JPEG-codec hardware IP core or CE systems using HLS                                                 |          |

|    | 6.1        | Problem formulation                                                                                                         | 67       |

|    | 6.2        | Overview of retinal biometric based hardware security approach                                                              | 67       |

|    | 6.3        | Demonstration on automatically detecting retinal feature points and generating retinal digital template                     | 73       |

|    | 6.4        | Demonstration on generating secured JPEG-codec IP using retinal biometric                                                   |          |

|    | 6.5        | Summary                                                                                                                     | 77       |

| 7. | Chapter    | 7                                                                                                                           | 78       |

|    |            | tion of security-cost tradeoff for signature driven security ms for optimal architecture of data-intensive hardware IPs     |          |

|    | 7.1        | Problem formulation                                                                                                         | 79       |

|    | 7.2        | Methodology for exploration of security-design cost                                                                         | 80       |

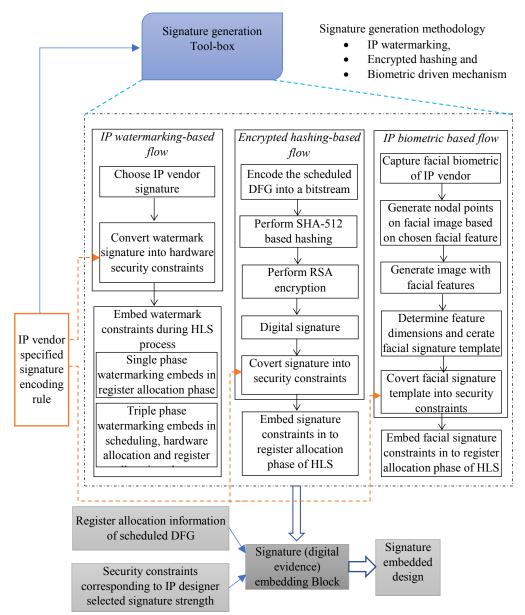

|    | 7.3        | tradeoff for obtaining low-cost architectural solution<br>Process flow of different signature driven security<br>algorithms | 90       |

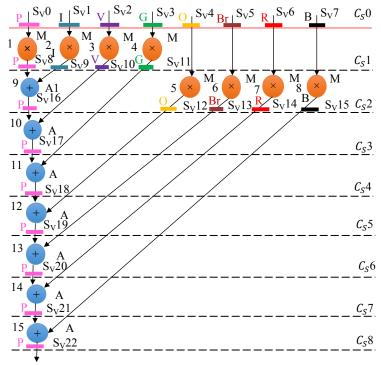

|     | 7.4<br>7.5   | Demonstration on generating low-cost and secure architectural solution for DCT 8-point application Summary                                        | 93         |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 8.  | Chapter      | •                                                                                                                                                 | 119        |

|     | Symmet       | rical Protection of Ownership Right's for IP Buyer and using Facial Biometric Pairing                                                             |            |

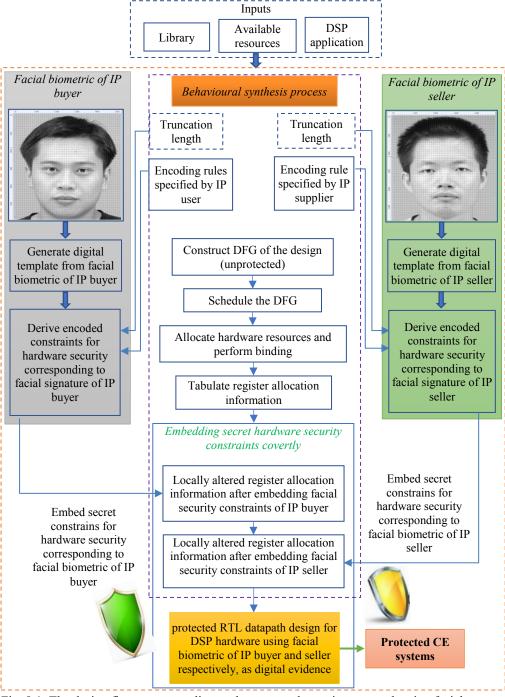

|     | 8.1<br>8.2   | Problem formulation Process for generating the secured design through                                                                             | 79<br>124  |

|     | 8.3          | embedding facial biometric of IP buyer Process for generating the secured design through embedding facial biometric of IP seller                  | 126        |

|     | 8.4          | Process for Nullifying false claim of IP rights and detecting IP piracy                                                                           | 129        |

|     | 8.5          | Summary                                                                                                                                           | 132        |

| 9.  | Chapter      | 9                                                                                                                                                 | 119        |

|     | Experim      | nental results and analysis                                                                                                                       |            |

|     | 9.1          | Results and analysis: Contact-less palmprint biometric for securing DSP co-processors used in CE systems                                          | 119        |

|     | 9.2          | against IP piracy Results and analysis: Double line of defense approach for securing DSP IP cores using structural obfuscation                    | 124        |

|     | 9.3          | and chromosomal DNA impression Results and analysis: Designing secured reusable convolutional IP core in CNN against piracy using                 | 126        |

|     | 9.4          | facial biometric based hardware security Results and analysis: Retinal biometric for designing secured JPEG-codec hardware IP core for CE systems | 129        |

|     | 9.5          | using HLS Exploration of security-cost tradeoff for signature driven security algorithms for optimal architecture of data-intensive hardware IPs  | 132        |

| 10. | Chapter      | 10                                                                                                                                                | 141        |

|     | Conclus      | ion and future work                                                                                                                               |            |

|     | 10.1<br>10.2 | Conclusion Future work                                                                                                                            | 141<br>143 |

|     | REFERI       | ENCES                                                                                                                                             | 144        |

# LIST OF FIGURES

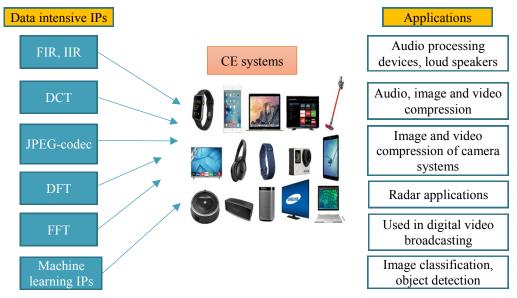

| Figure 1.1    | Different data intensive IPs and their applications                                                                      | 6  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|----|

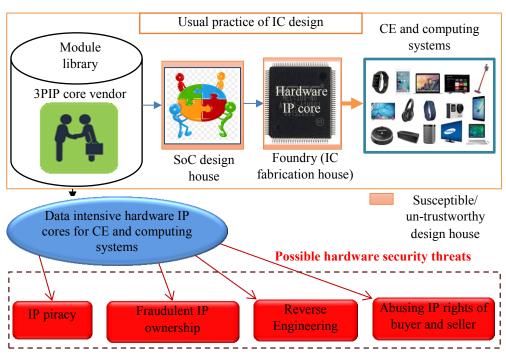

| Figure 1.2    | Possible hardware security threats in IC design chain                                                                    | 8  |

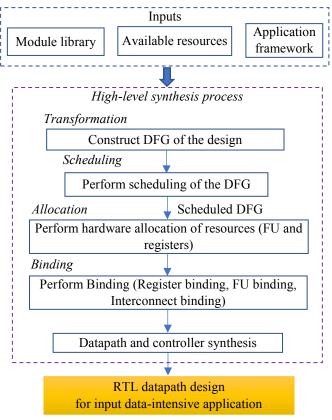

| Figure 1.3    | HLS design flow overview                                                                                                 | 12 |

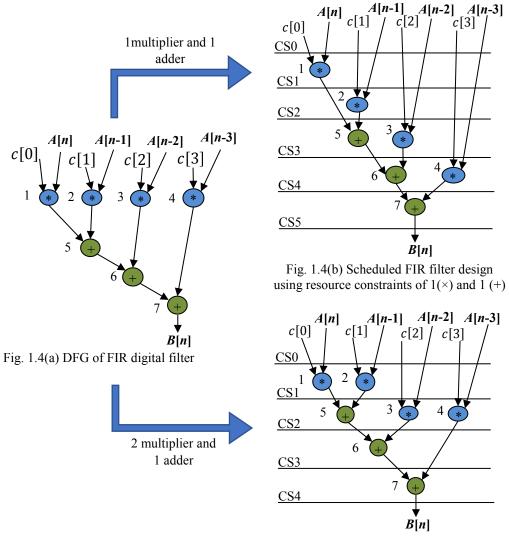

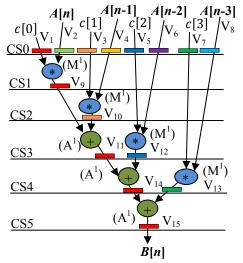

| Figure 1.4    | Scheduled DFG of FIR based on different resource constraint                                                              | 14 |

| Figure 1.5(a) | Scheduled and hardware allocated FIR filter design using resource constraints of $1(\times)$ and $1(+)$                  | 15 |

| Figure 1.5(b) | Scheduled and hardware allocated FIR filter design using resource constraints of $2(\times)$ and $1(+)$                  | 15 |

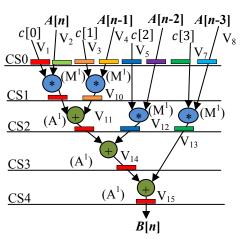

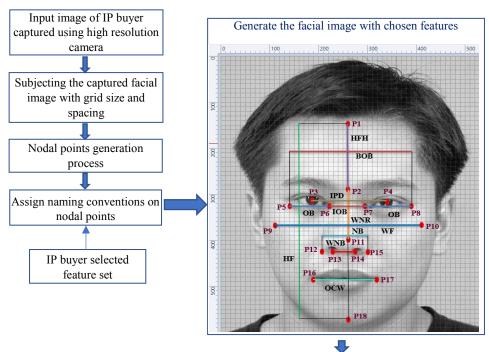

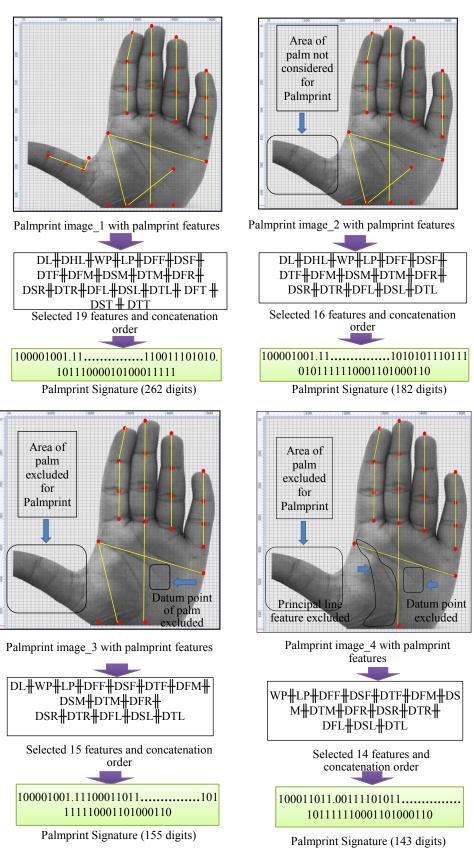

| Figure 3.1    | Overview of proposed contact-less palmprint biometric based hardware security methodology                                | 35 |

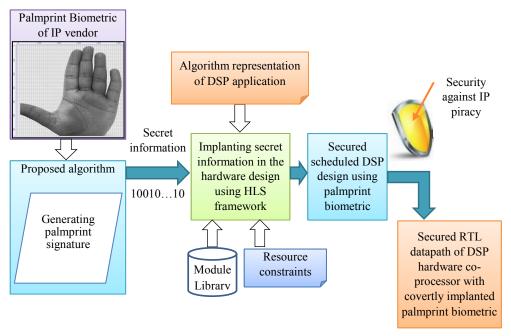

| Figure 3.2    | Flow of proposed palmprint biometric approach for securing DSP based co-processor designs during HLS                     | 38 |

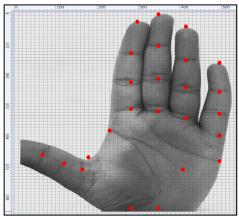

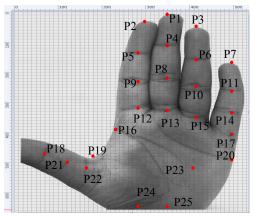

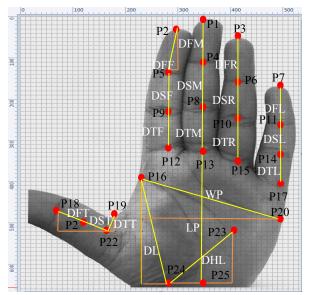

| Figure 3.3    | Nodal points on the sample palmprint with grid size and spacing                                                          | 40 |

| Figure 3.4    | Naming convention of nodal points on the palmprint image                                                                 | 40 |

| Figure 3.5    | Palmprint with chosen feature set                                                                                        | 41 |

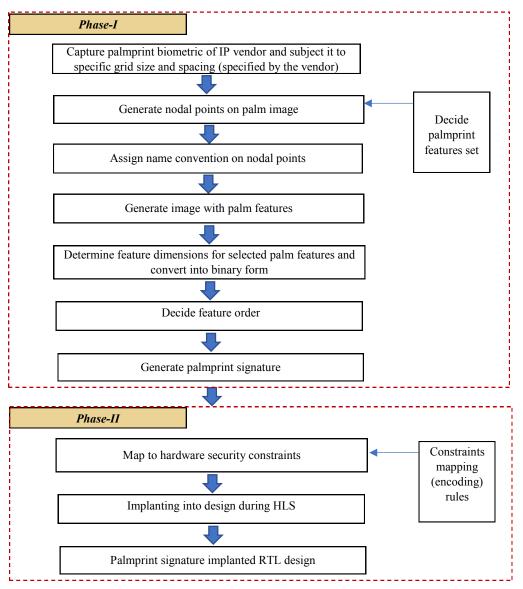

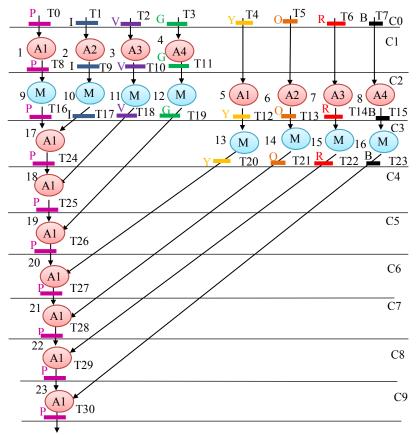

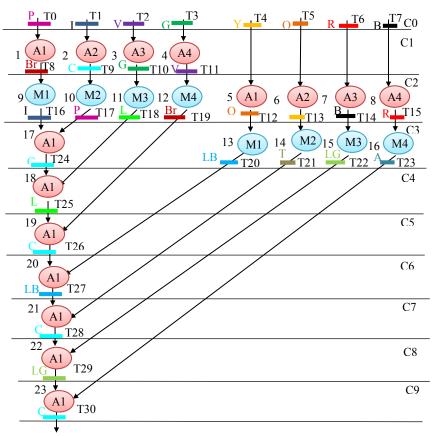

| Figure 3.6    | Scheduled FIR using 4*, 4+ before implanting palmprint                                                                   | 45 |

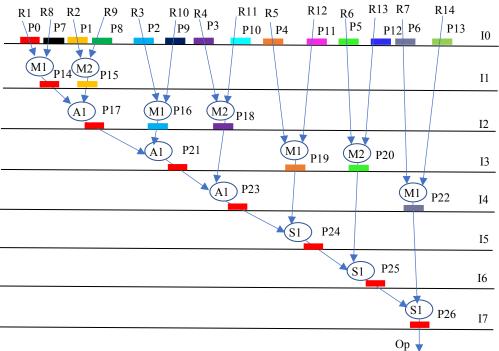

| Figure 3.7    | Scheduled FIR post implanting palmprint                                                                                  | 49 |

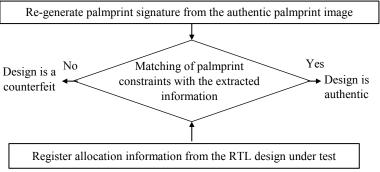

| Figure 3.8    | Detection of IP counterfeiting using proposed palmprint biometric                                                        | 50 |

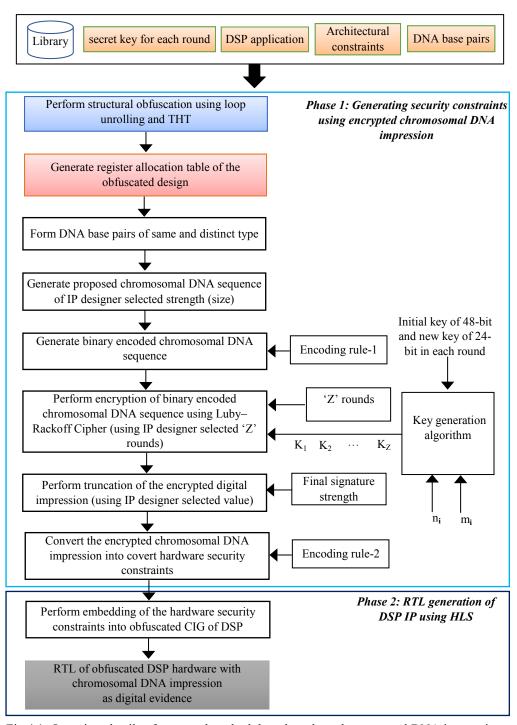

| Figure 4.1    | Overview details of proposed methodology based on chromosomal DNA impression                                             | 55 |

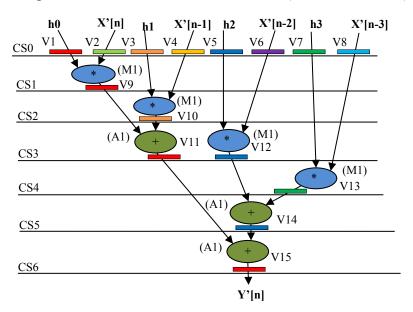

| Figure 4.2    | Scheduled DFG of FIR based on resource constraint (1M,1A)                                                                | 58 |

| Figure 4.3    | Scheduled, hardware allocated and binded DFG of FIR based on resource constraint (1M,1A) after high level transformation | 59 |

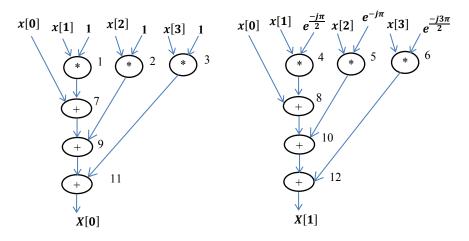

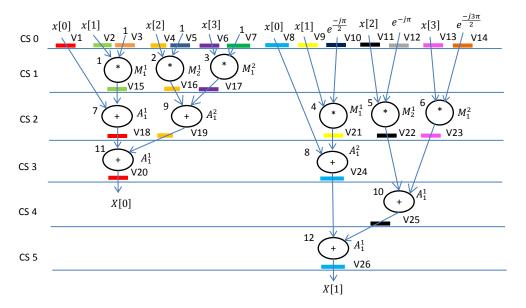

| Figure 4.4    | DFG of 4-point DFT computing two samples at a time                                                                       | 60 |

| Figure 4.5    | Scheduled DFG of obfuscated 4-point DFT based on resources constraints of 3M and 2A                                      | 60 |

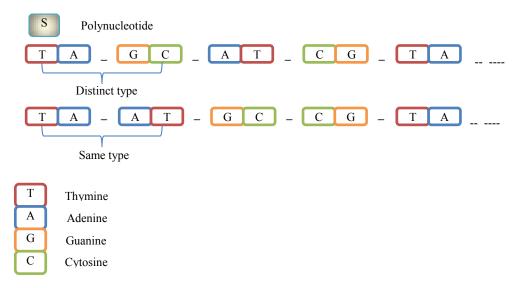

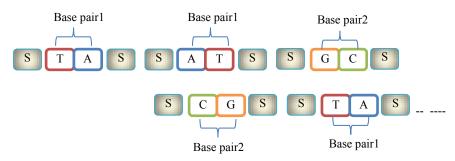

| Figure 4.6    | Proposed chromosomal DNA with distinct/same type base pairs                                                              | 61 |

| Figure 4.7    | Example of a possible chromosomal DNA sequence with base pairs and polynucleotide using proposed work                                                                                                                                                                                                                                                                                                                                              | 61  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

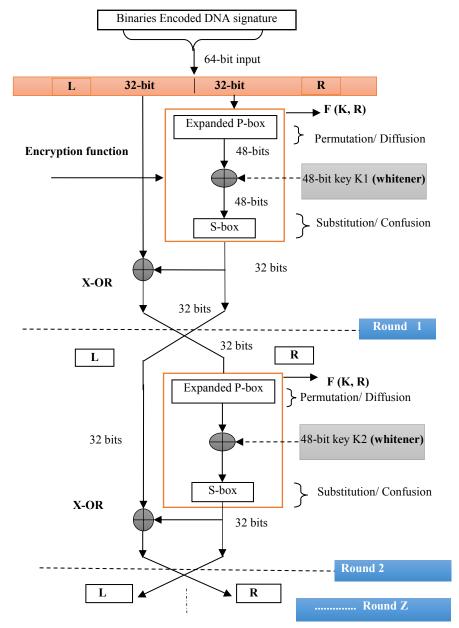

| Figure 4.8    | Encryption process using Feistel cipher                                                                                                                                                                                                                                                                                                                                                                                                            | 62  |

| Figure 4.9    | Key generation process in Feistel encryption framework                                                                                                                                                                                                                                                                                                                                                                                             | 63  |

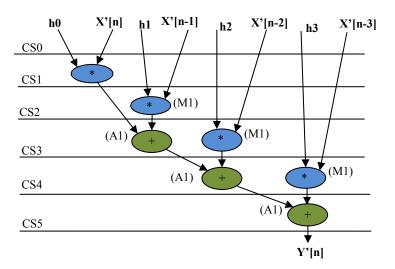

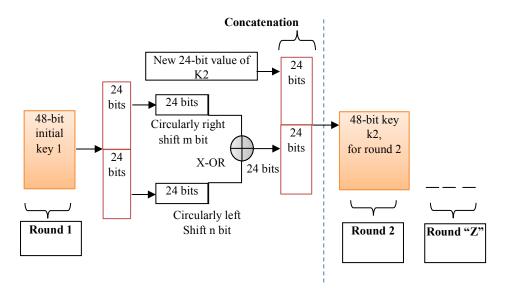

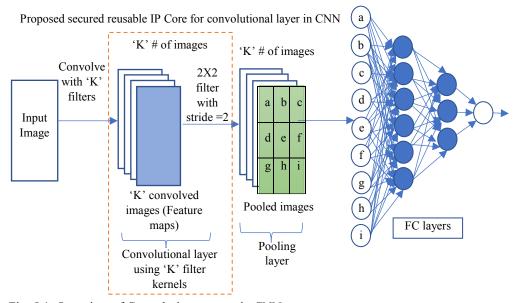

| Figure 5.1    | Overview of Convolution process in CNN                                                                                                                                                                                                                                                                                                                                                                                                             | 71  |

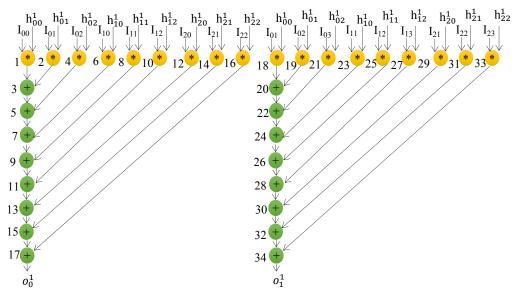

| Figure 5.2    | Data flow graph (DFG) of proposed reusable IP core with filter kernel of size 3x3 and UF=2                                                                                                                                                                                                                                                                                                                                                         | 80  |

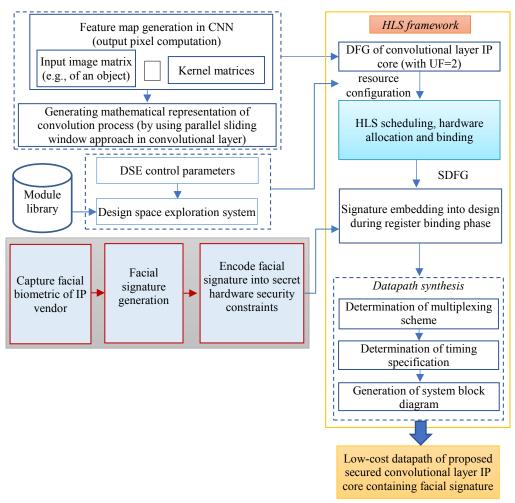

| Figure 5.3    | HLS flow of the proposed approach for designing secured convolutional layer IP core in CNN                                                                                                                                                                                                                                                                                                                                                         | 81  |

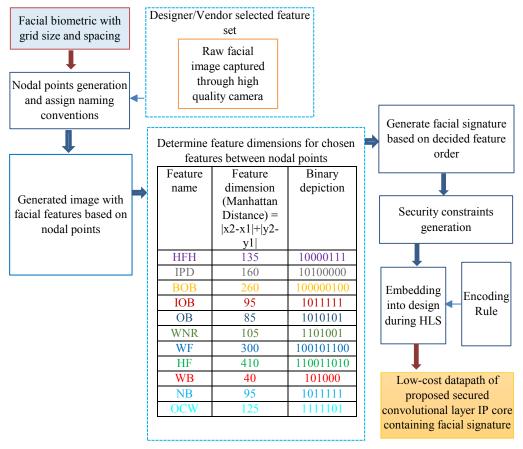

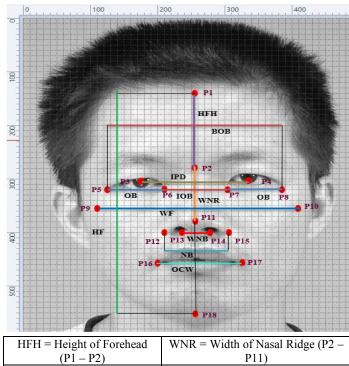

| Figure 5.4    | Details of facial biometric approach for securing convolutional layer IP core                                                                                                                                                                                                                                                                                                                                                                      | 82  |

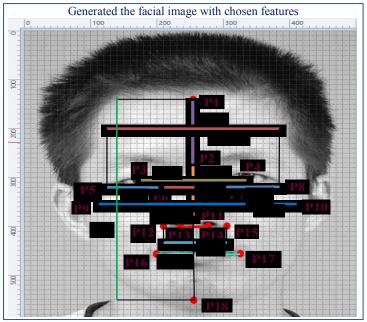

| Figure 5.5    | Generated image with facial features based on nodal points                                                                                                                                                                                                                                                                                                                                                                                         | 83  |

| Figure 5.6    | Scheduled DFG of proposed convolutional layer IP core with kernel of size 3x3 and UF=2 based on 1M, 1A resources                                                                                                                                                                                                                                                                                                                                   | 86  |

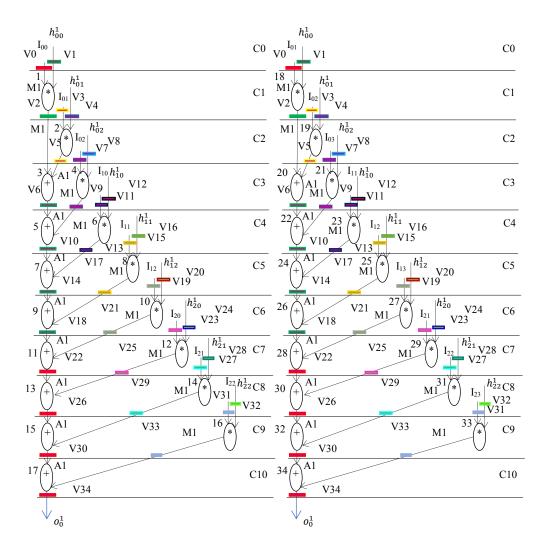

| Figure 5.7    | Post-embedding facial signature, proposed secured convolution layer kernel datapath for computing first output pixel $\mathbf{0_0^1}$                                                                                                                                                                                                                                                                                                              | 88  |

| Figure 5.8    | Post-embedding facial biometric, proposed secured convolution layer kernel datapath for computing second output pixel $0_1^1$                                                                                                                                                                                                                                                                                                                      | 88  |

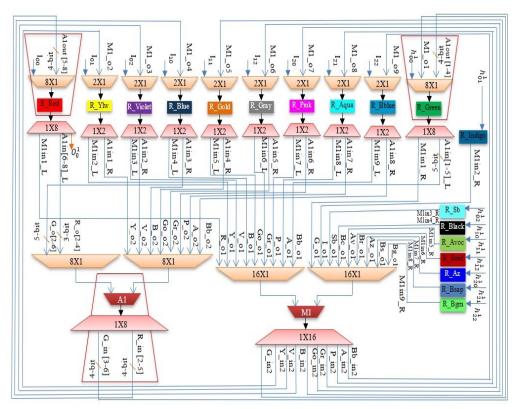

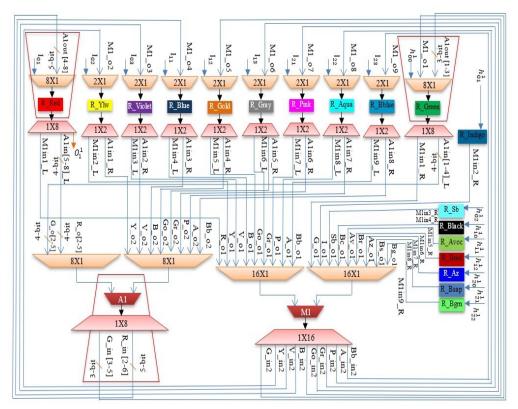

| Figure 5.9(a) | Proposed approach for convolutional layer IP Core design architecture secured using facial biometric                                                                                                                                                                                                                                                                                                                                               | 90  |

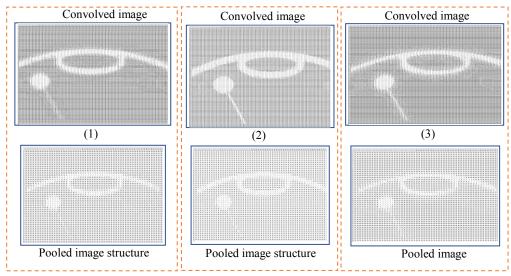

| Figure 5.9(b) | Output structure (image matrix representation) of convolved image and pooled image corresponding to different filters (1,2,3) used in proposed CNN convolutional layer                                                                                                                                                                                                                                                                             | 92  |

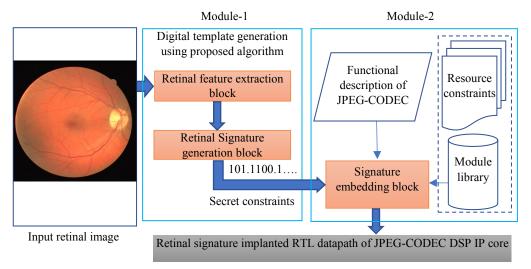

| Figure 6.1    | Overview of the proposed retinal biometric based hardware security methodology                                                                                                                                                                                                                                                                                                                                                                     | 99  |

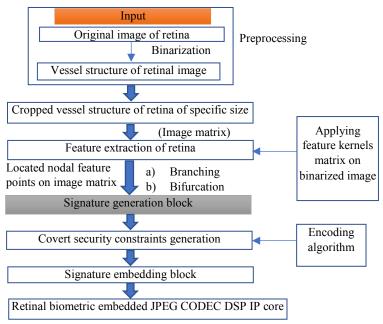

| Figure 6.2    | Details of the proposed retinal biometric based security methodology                                                                                                                                                                                                                                                                                                                                                                               | 101 |

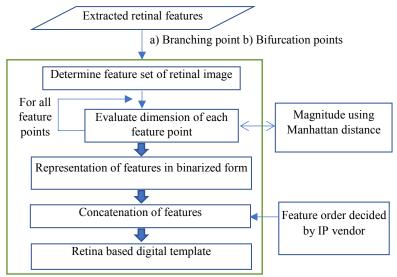

| Figure 6.3    | Details of signature generation block used for retinal biometric based digital template generation                                                                                                                                                                                                                                                                                                                                                 | 101 |

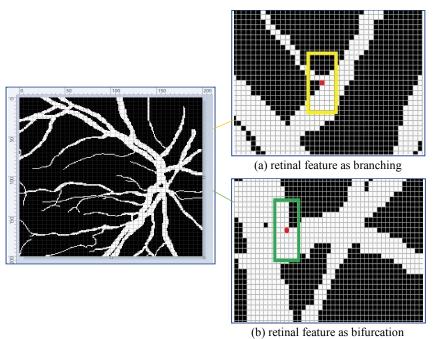

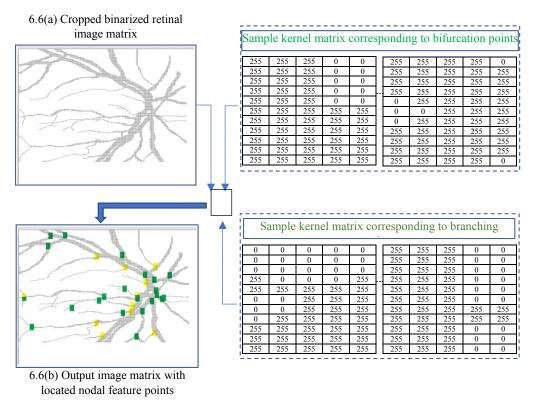

| Figure 6.4    | orientation of retinal features (a) representing branching nodal feature point with central pixel marked in red, is automatically detected using feature kernel matrix (as shown in Fig.6) corresponding to branching is represented in yellow (b) representing bifurcation nodal feature point with central pixel marked in red, is detected using feature kernel matrix (as shown in Fig.6) corresponding to bifurcation is represented in green | 104 |

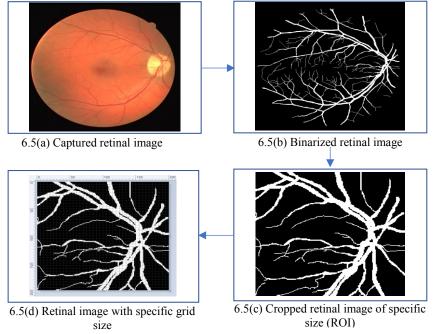

| Figure 6.5 Figure 6.6 | Placing ROI of retinal vessel structure into specific grid size (Image_1) Automatic detection of nodal feature points (bifurcation and branching) for Image 1                                                                                         | <ul><li>105</li><li>106</li></ul> |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Figure 6.7            | 2-D DCT coefficient matrix "I"; Matrix elements indicate eight- point DCT coefficients.                                                                                                                                                               | 113                               |

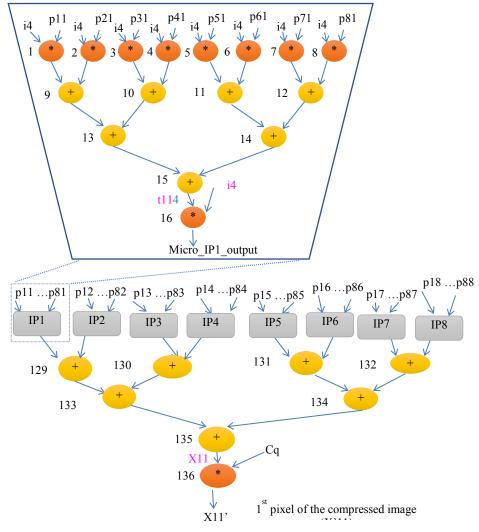

| Figure 6.8            | DFG of JPEG-CODEC IP core                                                                                                                                                                                                                             | 114                               |

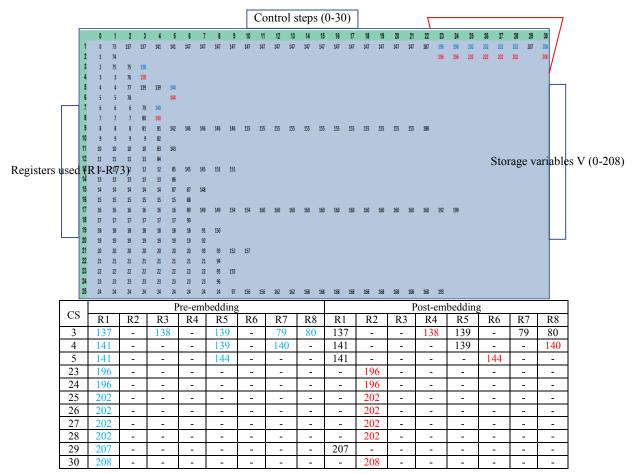

| Figure 6.9            | Register allocation framework post embedding retinal security constraints (pre and post embedding table represents changes due to security constraints). Note: For the sake of brevity, details of only 25 registers (out of 73) have been presented. | 116                               |

| Figure 6.10           | Pseudo code for isolating the pirated designs                                                                                                                                                                                                         | 118                               |

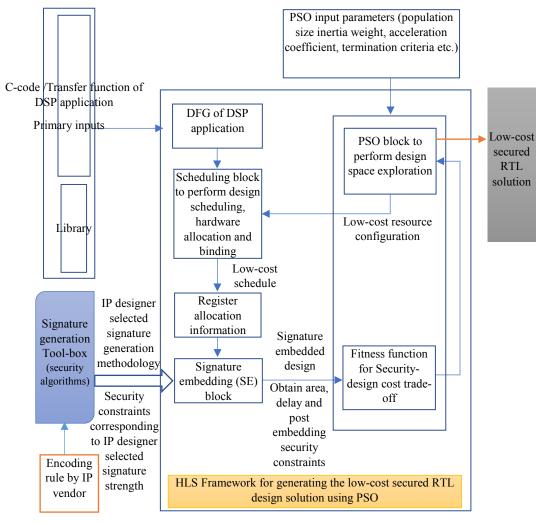

| Figure 7.1            | Details of the proposed methodology for performing security-design cost trade-off                                                                                                                                                                     | 127                               |

| Figure 7.2            | Process flow of signature generation methodologies and embedding their corresponding generated signature during HLS process                                                                                                                           | 129                               |

| Figure 7.3            | Details of the PSO based design space exploration                                                                                                                                                                                                     | 133                               |

| Figure 7.4            | Scheduled DFG of 8-point DCT core using one adder (A) and four multipliers (M)                                                                                                                                                                        | 134                               |

| Figure 8.1            | The design flow corresponding to the proposed security approach using facial biometric                                                                                                                                                                | 143                               |

| Figure 8.2            | Process for generating biometric information corresponding to facial features of IP buyer                                                                                                                                                             | 145                               |

| Figure 8.3            | Scheduled DFG of IIR filter corresponding to resources one adder, two multipliers and one subtractor                                                                                                                                                  | 148                               |

| Figure 8.4            | Facial image with selected facial features corresponding to IP supplier                                                                                                                                                                               | 149                               |

| Figure 9.1            | Variation in the final palmprint signature with respect to different size of palmprint features set of the same palm                                                                                                                                  | 154                               |

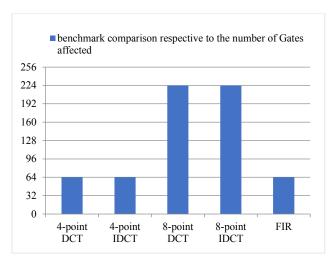

| Figure 9.2            | Strength of obfuscation of proposed approach                                                                                                                                                                                                          | 159                               |

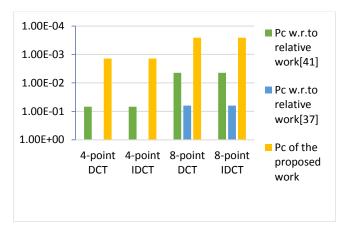

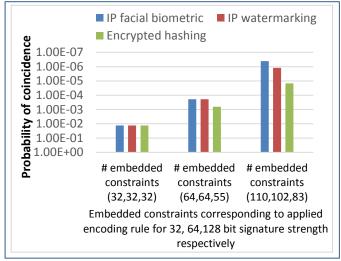

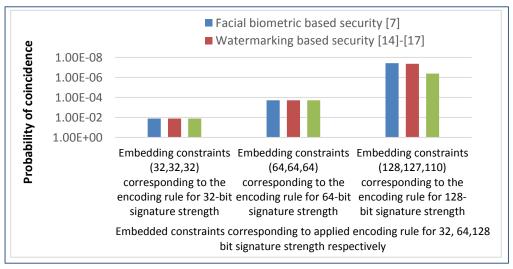

| Figure 9.3            | Comparison of probability of coincidence (Pc)                                                                                                                                                                                                         | 160                               |

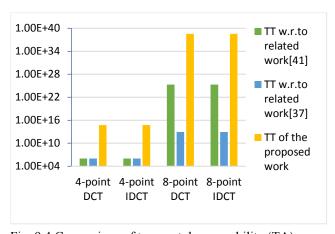

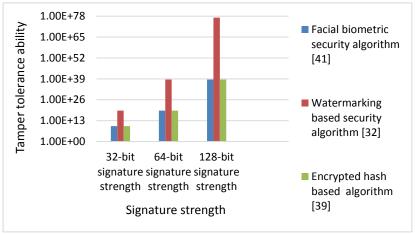

| Figure 9.4            | Comparison of tamper tolerance ability (TA)                                                                                                                                                                                                           | 160                               |

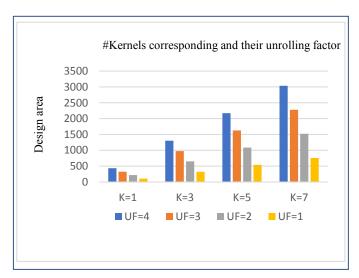

| Figure 9.5            | Impact of number of CNN convolutional filter kernels 'K' and unrolling factor 'UF' on design area                                                                                                                                                     | 165                               |

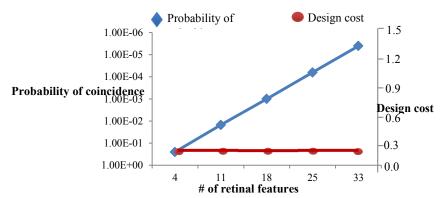

| Figure 9.6            | Pc- design cost trade-off for JPEG-codec for different<br>number of retinal features of same retinal image<br>(Image_1)                                                                                                                               | 169                               |

| Figure 9.7  | Pc comparison of security methodologies for 8-point DCT application                              | 172 |

|-------------|--------------------------------------------------------------------------------------------------|-----|

| Figure 9.8  | Pc comparison of security algorithms for ARF framework                                           | 172 |

| Figure 9.9  | Tamper Tolerance ability comparison of security algorithms for different signature strengths     | 172 |

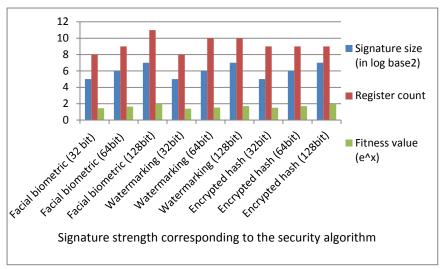

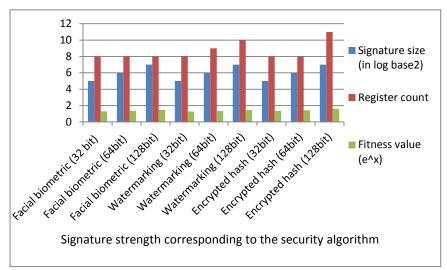

| Figure 9.10 | Impact of signature strength on fitness value and register count in 8-point DCT application [84] | 175 |

| Figure 9.11 | Impact of signature strength on fitness value and register count in ARF application [84]         | 175 |

# LIST OF TABLES

| Table 3.1 | Selected palmprint features, corresponding nodal points and their coordinates                                                        | 42  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2 | Feature dimension and corresponding binary representation of palmprint features chosen by IP vendor                                  | 43  |

| Table 3.3 | Register assignment of storage variables (T0-T30) of FIR digital filter pre-implanting palmprint signature                           | 46  |

| Table 3.4 | Mapping rules for generating palmprint security constraints                                                                          | 46  |

| Table 3.5 | Register assignment of storage variables of FIR digital filter post implanting palmprint signature                                   | 48  |

| Table 4.1 | Register allocation in obfuscated CIG of 4-point DFT (before implantation of chromosomal DNA)                                        | 65  |

| Table 4.2 | Register allocation in obfuscated CIG of 4-point DFT (after implantation of chromosomal DNA)                                         | 65  |

| Table 5.1 | Decision rule (embedding of a specific 14-bit long signature part into a particular datapath of k <sup>th</sup> kernel is            | 84  |

| Table 5.2 | shown using color mapping) Register allocation of proposed convolutional layer IP core (partial view post implantation)              | 87  |

| Table 6.1 | Determining feature dimensions and generating retinal signature                                                                      | 108 |

| Table 6.2 | ASAP Scheduling (3+, 3*) of Macro IP of JPEG-codec                                                                                   | 111 |

| Table 6.3 | Encoding for generating the secret security constraints                                                                              | 111 |

| Table 7.1 | Qualitative comparison between the security approaches                                                                               | 132 |

| Table 7.2 | Register allocation of 8-point DCT (pre-embedding)                                                                                   | 135 |

| Table 7.3 | Register allocation of 8-point DCT (post-embedding, in case of IP watermarking approach)                                             | 137 |

| Table 7.4 | Register allocation of 8-point DCT application ( <i>Post embedding in case of encrypted hash-based approach</i> )                    | 139 |

| Table 7.5 | Register allocation of 8-point DCT application ( <i>Post embedding in case of facial biometric approach</i> )                        | 139 |

| Table 8.1 | Register allocation information post embedding the facial biometric driven security constraints corresponding to IP buyer and seller | 151 |

| Table 9.1  | Variation in Pc of FIR filter design for different size of palmprint signature of same palm                                     | 156 |

|------------|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 9.2  | Comparison of Pc w.r.t related work [40]                                                                                        | 156 |

| Table 9.3  | Comparison of Pc w.r.t. related work [37]                                                                                       | 156 |

| Table 9.4  | Comparison of proposed approach with digital signature [31]                                                                     | 156 |

| Table 9.5  | Comparison of proposed approach with digital signature based watermarking approach [33]                                         | 157 |

| Table 9.6  | Comparison of tamper tolerance (TT) w.r.t. related work [40]                                                                    | 157 |

| Table 9.7  | Design cost pre and post embedding palmprint biometric constraints                                                              | 157 |

| Table 9.8  | The Pc of the proposed approach indicating strength of digital evidence                                                         | 159 |

| Table 9.9  | Obfuscated design cost pre and post embedding encrypted chromosomal DNA impression constraints (32, 64, 128 bits)               | 161 |

| Table 9.10 | Execution time of proposed approach                                                                                             | 161 |

| Table 9.11 | Number of executions for convolution operation                                                                                  | 162 |

| Table 9.12 | Number of pixels computed in parallel for different kernel sizes                                                                | 162 |

| Table 9.13 | Resources in the RTL datapath of CNN convolutional layer reusable IP core (pre and post embedding facial biometric constraints) | 163 |

| Table 9.14 | Comparison of Pc with respect to related approach [39], [37] for CNN convolutional layer IP core                                | 164 |

| Table 9.15 | Percentage reduction in Pc value achieved using proposed approach compared to related works [39], [37]                          | 164 |

| Table 9.16 | Comparison of tamper tolerance with respect to related approach [39] for CNN convolutional layer Reusable IP core               | 164 |

| Table 9.17 | Variation in Pc for different size of retinal signature of same retina (Image_1)                                                | 166 |

| Table 9.18 | Variation in Pc and TT for different retinal images                                                                             | 166 |

| Table 9.19 | Comparison of Pc w.r.t related work [40], [41], [39]                                                                            | 167 |

| Table 9.20 | Comparison of TT w.r.t related works [40], [41], [39]                                                                                                                                       | 167 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 9.21 | JPEG-codec IP core design cost pre and post embedding retinal biometric constraints (Image_1)                                                                                               | 168 |

| Table 9.22 | JPEG-codec IP core design cost pre and post<br>embedding retinal biometric constraints for different<br>retinal images                                                                      | 168 |

| Table 9.23 | Implementation time of the proposed retinal biometric based hardware security approach                                                                                                      | 169 |

| Table 9.24 | Details of the security constraints, fitness function, global best solution and average exploration time of the proposed approach for 8-point DCT w.r.t. various security algorithms [84]   | 173 |

| Table 9.25 | Details of the security constraints, fitness function, global best solution and average exploration time of the proposed approach for ARF framework w.r.t. various security algorithms [84] | 173 |

| Table 9.26 | The details of DSP hardware units obtained during trade-off exploration (security-design cost)                                                                                              | 174 |

| Table 9.27 | Pc analysis corresponding to facial signature of IP buyer w.r.t. [80]                                                                                                                       | 174 |

| Table 9.28 | Pc analysis corresponding to facial signature of IP seller w.r.t. [80]                                                                                                                      | 174 |

| Table 9.29 | Design cost of the proposed approach post embedding facial biometric signature of IP buyer and then of IP seller into the design                                                            | 175 |

# **NOMENCLATURE**

| X                | Number of colors in the CIG or the number of registers into register allocation table               |

|------------------|-----------------------------------------------------------------------------------------------------|

|                  |                                                                                                     |

| Z                | Number of constraint edges implanted into the CIG                                                   |

| Pc               | Probability of coincidence                                                                          |

| W                | Number of types of digits in the signature                                                          |

| Pc               | Probability of coincidence                                                                          |

| S                | Signature size                                                                                      |

| $A_d/K_d$        | Design area                                                                                         |

| $L_d/T_d$        | Design latency                                                                                      |

| A <sub>m</sub>   | Maximum design area                                                                                 |

| L <sub>m</sub>   | Maximum design latency                                                                              |

| Z                | Number of encryption rounds                                                                         |

| O <sub>y</sub>   | Output value of each element/pixel corresponding to output feature map                              |

| D                | Number of padding bits                                                                              |

| q                | Stride                                                                                              |

| K                | Number of filter kernels                                                                            |

| S                | The size of the filter                                                                              |

| V                | Input volume image size                                                                             |

| TT               | Tamper tolerance                                                                                    |

| Cq               | Quantization coefficient                                                                            |

| $C_{T}$          | Terminating criteria                                                                                |

| $P_{S}$          | Population size                                                                                     |

| S<br>Gb          | Global best resource                                                                                |

| S <sub>id</sub>  | The current position of i <sup>th</sup> particle in dimension 'd'                                   |

| α                | Minimum resource value                                                                              |

| β                | Maximum resource value                                                                              |

| γ                | Any random number value of resources between 'α' and 'β'                                            |

| vid              | The velocity of i <sup>th</sup> particle d <sup>th</sup> dimension in current or previous iteration |

| vid <sup>+</sup> | The velocity of i <sup>th</sup> particle d <sup>th</sup> dimension in next iteration                |

| $S_{lb}$         | Local best resource                                                                                 |

| $S_{lbi}$        | Local best solution of the ith particle                                                             |

| $Z_c$            | Design cost                                                                                         |

|                  |                                                                                                     |

# **ACRONYMS**

| HLS  | High Level Synthesis                                             |

|------|------------------------------------------------------------------|

| VLSI | Very Large Scale Integration                                     |

| IP   | Intellectual Property                                            |

| DSP  | Digital Signal Processor                                         |

| CE   | Consumer Electronics                                             |

| IC   | Integrated Circuits                                              |

| SoC  | System on Chip                                                   |

| RTL  | Register Transfer Level                                          |

| VHDL | Very High Speed Integrated Circuit Hardware Description Language |

| GDS  | Graphic Database System                                          |

| ALU  | Arithmetic Logic Unit                                            |

| DFG  | Data Flow Graph                                                  |

| CDFG | Control Data Flow Graph                                          |

| SDFG | Scheduled Data Flow Graph                                        |

| FSM  | Finite State Machine                                             |

| RE   | Reverse Engineering                                              |

| CS   | Control Step                                                     |

| CIG  | Colored Interval Graph                                           |

| UF   | Unrolling Factor                                                 |

| 3PIP | 3 <sup>rd</sup> party Intellectual Property                      |

| ASIC | Application Specific Integrated Circuit                          |

| PSO  | Particle Swarm Optimization                                      |

| DSE  | Design Space Exploration                                         |

| FU   | Functional Unit                                                  |

| HLT  | High Level Transformation                                        |

| opn  | Operation                                                        |

| LU   | Loop Unrolling                                                   |

| THT  | Tree Height Transformation                                       |

| ROE  | Redundant Operation Elimination                                  |

| LICM | Loop Invariant Code Motion                                       |

| SHA  | Secure Hash Algorithm                                            |

| DCT   | Discrete Cosine Transform         |

|-------|-----------------------------------|

| IDCT  | Inverse Discrete Cosine Transform |

| DWT   | Discrete Wavelet Transform        |

| FFT   | Fast Fourier Transform            |

| FIR   | Finite Impulse Response           |

| IIR   | Infinite Impulse Response         |

| DFT   | Discrete Fourier Transform        |

| JPEG  | Joint Photographic Expert Group   |

| MPEG  | Moving Picture Expert Group       |

| CE    | Consumer electronics              |

| Mux   | Multiplexer                       |

| Demux | Demultiplexer                     |

| 3PIP  | Third-party IP                    |

| DNA   | Deoxyribonucleic acid             |

| CNN   | Convolutional neural network      |

| MAC   | Multiply accumulate               |

| FPGA  | Field programmable gate array     |

| SE    | Signature embedding               |

## **Chapter 1**

## Introduction

We are the most privileged human generation as we live in the era of smart technology; Thanks to our scientists and researchers. In this era, contribution of electronics systems has played a pivotal role in achieving the desired goal and fulfilling the vision of availing smart and affordable technology to everyone. In this modern era where everyone intends to have faster and lowcost processing of their tasks either in regards of an application or a system/device, need of developing such systems/devices is prevailing. One can easily observe several consumer electronics and computing systems such as smart phones, smart watches, tablets, digital cameras, computers and audio headsets etc. are the part of our life style and also have become the necessity. These computing/CE systems are ubiquitously used for performing the various tasks/applications based on image processing, audio-video processing etc. However, underneath these computing/CE systems, there functions a systemon-chip (SoC). A SoC is designed using various modules such as functional blocks, memory units and memory controller and different peripherals for wireless and wired communication etc. In deployed practice, instead of designing a SoC from scratch, its various modules/cores are purchased from third-party IP (3PIP) vendors or designers. And, this kind of system design paradigm is called as core-based design paradigm [1]-[11].

In computing devices and systems, for performing data-intensive tasks, hardware accelerators are used to achieve higher performance and efficacy by accelerating the underlying process [12]. During the acceleration process of an application, certain computing tasks are offloaded into specialized hardware components typically known as hardware accelerators or intellectual property (IP) core. A hardware IP is a reusable unit (block of data/logic) of computational function, Boolean logic, register transfer level (RTL) or a gate structure, and is also known as the intellectual property of a designer. There are various applications for example, cryptographic applications are performed using cryptographic IP cores while fingerprint, face recognition and handprint biometric require digital signal processing (DSP) and image processing IP

cores. Further Artificial Intelligence (AI) applications require AI cores, sound processing via sound card and digital signal processing via digital signal coprocessor etc. Further, in computing and CE systems, different applications such as image compression-decompression, audio de-noising and video processing etc. (which are data intensive in nature) are facilitated using different IP cores with higher efficacy and at lower design cost. The IP cores employ the execution of different algorithms such as discrete cosine transformation (DCT), fast fourier transform (FFT), finite impulse response etc., used for digital signal processing (DSP), machine learning and multimedia processing etc., which are highly data-intensive in nature [13], [14].

Therefore, due to design complexity, design cost and time to market pressure, these applications frameworks are realized as reusable IP cores. This therefore enables cost reduction and elevates design turnaround time. Therefore, current generation system on chip (SoC) designers amalgamate reusable IP cores imported from multiple IP vendors/manufacturers. These IP cores are mass-produced, tested and verified by various companies and the IP supply chain is distributed worldwide.

Further, from the perspective of researcher as well as user, it becomes equally crucial to understand the process of designing and developing such systems. The design cycle of such systems involves several design phases and different entities. The different design phases may be categorized based on design complexity, designing cost and flexibility. Therefore, it becomes crucial to have the understandings of different design phases. Further, the involved entities can also be categorized in terms of their role in the design chain and trustworthiness. Different entities (third party IP vendors, system integrator, and foundry) get involvement in the IC design chain. This helps in sustaining the IC design process at lesser cost, lower design complexity and lower time requirement [12]. However, it also enforces to incorporate security measures to safeguard the designs against security hazards for ensuring their safe usage to end consumer.

However, the involvement of distinct entities (or offshore design houses) in the design chain raises the issue of trust [15]-[26]. This is because an adversary or attacker in an untrustworthy design house may realize his/her malicious intents of IP piracy. Additionally, security against fraudulent claim of IP ownership, implantation of hidden malicious logic by reverse engineering the design and protection of IP rights of IP buyer and seller are crucial. As the DSP, multimedia and machine learning based IP cores possess significant role in CE systems, mission critical tasks, IoT devices and healthcare applications, therefore their security perspective cannot be overlooked. This is because integration of a pirated IP version into SoCs of such systems may lead safety and integrity hazards to end consumer.

This chapter in a nutshell discusses the background on the various key aspects that the proposed hardware security techniques are developed around. The first section provides the background on different design abstraction level of an IP core. Further, the second section provides an overview of DSP, machine learning and multimedia-based data-intensive applications and corresponding algorithmic representations. The third section discusses the various threats to reusable data intensive hardware IP cores. The fourth section provides a background on high level synthesis (HLS) process and its role in designing low-cost and secured of reusable hardware IPs. At the end, the fifth section presents the thesis organization.

# 1.1. Different design abstraction levels and corresponding form of hardware IP core

Due to higher complexity involved, it is crucial to design an IP core from higher abstraction level of IC design process. This is because, the higher abstraction level offers lesser complexity and higher flexibility to incorporate the low-cost architecture and robust security mechanism than the lower design abstraction levels. The design abstraction levels are as follows [81], [82]: (a) system/behavioral level (b) register transfer level (c) gate level or netlist level and (d) layout or transistor level.

The top most design abstraction level is behavioral level. At this level design/application is described based on the respected inputs, output and

transfer function or behavioral description. The behavioral/mathematical function of an application is accepted as input for transforming it into next level design. Therefore, the algorithmic description of the design/application is transformed into register transfer level using high level synthesis (HLS). Additionally, integrating the security mechanism during higher abstraction also is less complex as well as ensures the security at subsequent lower abstraction level design versions. The design obtained post HLS (RT level design version) is termed as soft IP. In other words, IP cores which are generally available as synthesizable register transfer level code in the form of either schematic design (.bdf file) or hardware description language (.vhd/.vhdl file), are called as soft IP. One of the advantages of the soft IP cores is that, they offer a chip designer the flexibility to modify the design parameters as per the requirement.

Further, the next design abstraction level is gate level or netlist level. IP design at this level is obtained by transforming register transfer (RT) level design into gate level design using logic synthesis or RTL synthesis. It describes the design interconnectivity in terms of various cells that are present with in it and the output of synthesis process at logic level. The gate level netlist of the design is called as firm IP core. This IP version is a technology dependent and is lesser modifiable than a soft IP core. RTL and gate-level netlist both allow post synthesis processing steps such as placement, routing, and downloading into reconfigurable platforms such as (field programmable gate arrays) FPGAs.

Subsequently, the next design abstraction level is transistor level. IP design at this level is obtained by transforming gate level design into layout level design using layout synthesis. The IP design version at this level is known as hard IP. hard IP cores are generally available as a layout format (fixed masked layout) of chip designs in the graphic data system (GDS) or layout editor documentation (LEF) format. Unlike soft IP cores, hard IPs cannot be modified by chip designers or system integrators. Further, demerit of a hard IP design is that it does not allow to be used in another foundry (for fabrication) for which it is not targeted to. This is because, design at layout level comprises of process foundries and a design rule, which incapacitates the use of layout in

another foundry except to whom it was targeted. Therefore, due to more flexibility (in terms of modifying functionality) and greater portability (can be reused), soft IPs are preferred over Hard IPs. However, soft IP cores are exposed to greater IP protection risk than hard IPs as they can be modified by system integrators. Thus, it is interpretable that an IP core is designed and sold into the market in one of its forms such as (i) soft IP core (ii) firm IP core (iii) hard IP core.

However, based on the computational capability and design size, they are categorized into two different types: micro-IPs and macro-IPs (are essentially bigger logic). Logic gates, combinational and sequential circuits (register and memory) are some of the examples of micro-IPs. On the other hand, digital signal processors (DSPs), central processing units (CPUs) and application specific cores such as joint photographer expert group (JPEG) engines, moving picture expert group (MPEG) engines, digital filters like finite impulse response (FIR) filter and infinite impulse response (IIR) filter, falls under the category of macro-IPs. These DSP cores facilitate several applications like image compression-decompression, digital data filtration and audio processing etc., which are computationally intensive in nature.

# 1.2. DSP, machine learning and multimedia-based applications and their algorithmic representation

In the DSP co-processors, there functions a DSP algorithm for performing the corresponding to application/task. Some widely used DSP algorithms are discrete cosine transform (DCT), discrete Fourier transform (DFT), fast Fourier transform (FFT), Haar wavelet transform (HWT), discrete wavelet transform (DWT), inverse discrete cosine transform (IDCT). DCT is used while converting an image from spatial domain to its frequency domain. Further, it is the basic fundamental algorithm for performing image compression-decompression in JPEG-codec co-processors. DFT, FFT are used for representing a discrete signal from its time domain to frequency domain. HWT is used for transforming the waveform of a signal from time domain to time-frequency. It is widely used for both lossy and loss-less signal and image compression-based applications. DWT is used for performing the denoising of

Fig. 1.1 Different data intensive IPs and their applications

the real signal by decomposing it. It basically decomposes a digital signal for obtaining finer frequency and coarser time resolution based on different subbands. It is the basic fundamental algorithm for performing image compression in JPEG2000. Further, digital filters like finite impulse response (FIR) filter and infinite impulse response (IIR) filter have wide utility in modern electronic systems. For example, they are used in speech processing, telecommunication, removal of attenuation of selected frequencies etc. Different data intensive hardware IP cores and their usages are shown in Fig. 1.1.

Further, machine learning IP cores are used for performing different tasks related to it. On the other hand, in multimedia processors, there functions multimedia processing algorithms such as joint photographic experts group compression-decompression (JPEG-codec) and moving picture experts group (MPEG) etc. JPEG is used for performing the image compression. In order to do so, it firstly converts an input image from spatial domain to frequency design. Subsequently, by performing the quantization (discarding less important frequency components) it results into a compressed image. It is widely used in medical imaging, digital camera systems etc.

In order to generate an application specific processor of data-intensive applications, its algorithmic or behavioral description is processed as input for the synthesis process [12], [91]. The algorithmic description can be of various forms such as a C/C++ code or transfer function or a mathematical equation

representing input-output relationship) etc. For example, an algorithmic description of FIR application in the form of a mathematic function is given as follows [81]:

$$\mathbf{B}[\mathbf{n}] = \sum_{i=0}^{N} c[i] * \mathbf{A}[\mathbf{n} - \mathbf{i}]$$

(1.1)

Where, N represents the order of the FIR filter. Further, the mathematical equation based on the order of FIR filter, can be represented as follows:

$$B[n] = c[0] * A[n] + c[1] * A[n-1] + c[2] * A[n-2] + \dots + c[N] * A[n-N]$$

(1.2)

Where, A[n] to B[n] represents the current input-output and A[n-1], A[n-2] represents the previous input values and, c[0], c[1] ... c[N] indicates input coefficients of the FIR. This mathematical description is exploited for generating the application specific hardware co-processor design of FIR filter.

#### 1.3. Threats to reusable data intensive hardware IP cores

As discussed earlier, in the deployed semiconductor design chain, various offshore entities such as a 3PIP vendor, a system integrator and foundry houses are involved. This is to speed up the design process for attaining the goals of low-design cost, shorter design time and time to market etc. Therefore, an IP cores may be sold/supplied by different IP vendors. Based upon the design requirements, these IPs are supplied to an SoC integrator for their integration into SoC design or else they are directly supplied to foundry houses for fabrication as a standalone IC. Thus, after the integration of IPs at SoC integrator house, it is supplied to foundry house(s) for their fabrication. This renders the asymmetric nature of business model. In other words, the data flow in the design cycle in unidirectional e.g., from IP vendor to SoC integrator house to foundry house. More explicitly, there can be multiple IP vendors for providing the IP design and there can also be multiple foundry houses, where fabrication can be done. This involvement of multiple entities in the IC design chain, renders it vulnerable to different hardware security threats [15]-[26], [27]-[36], [53], [54]. The different entities involved in design chain and possible hardware security threats are shown in Fig. 1.2.

In year 2007 and 2008, joint intellectual property rights enforcement operations (I and II respectively) was carried out by United States Customs and Border Protection (CBP) and European Union Customs. They seized lakhs of counterfeited ICs and computer network components. However, this is not the complete figure of the counterfeited parts that might have been supplied in that period. In 2010, VisionTech company owner and its administrative manager was charged for deliberately involving in trafficking of counterfeited goods [88]. They were found responsible for importing thousands of shipments of counterfeited semiconductors into the United States. They targeted the US Navy and defense contractors. When this conspiracy got detected, it was realized that how a rogue broker attempted to compromise national security and life of countless individuals on risk nearly for half a decade. It was estimated that VisionTech cause the damage to 21 semiconductor companies by supplying them the counterfeited components. In 2012, a market research firm 'iHS iSuppli' reported that the counterfeited components cause multibillion-dollar loss to the global electronics supply chain. In 2016, Dutch customs and Europian Union (EU) executed an operation for targeting the semiconductors supply into EU from China and Hong Kong. They seized more than one million counterfeited devices with in few weeks span. Further, the report of world semiconductor council (WSC)

Fig. 1.2 Possible hardware security threats in IC design chain

published in 2018, states that counterfeited components significantly jeopardized security and economy. Pirated components are responsible for wastage of billion dollars of semiconductor companies per year to assure the reliable operation of customer applications [89], [90]. However, it is not possible to accurately determine the impact of semiconductor counterfeiting. But the data or reports surface the criticality of the issue. This raises serious concern of trust in the global IC supply chain. A brief discussion on the hardware security threats is as follows:

### 1.3.1 IP Core Piracy

The design process of an IP core for multi-modal CE designs involves many man-hours of research, investment, validation and effort. Therefore, in the modern design cycle, multiple offshore entities are involved to cut down the overall design cost, design complexity and time-to-market. However, this involvement of offshore design houses or foundries in the design chain has posed the serious hardware threats of IP piracy. A SoC integrator may purchase IP cores (to be integrated) either directly from an IP vendor or else from a broker (acting as a middleman between IP designer and the SoC integrator). However, a national interest or yearn of earning illegal income may trigger a rouge IP supplier to infuse pirated or fake components (IPs) in the design supply chain. The use the fake components (pretending to be genuine) in the SoCs of CE devices may adversely impact both CE system integrator and end user. Further, ensuring security against IP piracy threat is highly important for consumers because of following reasons: (i) counterfeited designs are not rigorously tested for ensuring reliability and safety (ii) counterfeit IPs contain secret malicious logic (hardware Trojans) hidden inside. These infected IPs or ICs are unreliable and unsafe for end consumers, when integrated in CE systems. Therefore, it is crucial to discern between authentic and fake IP versions for enabling the use of only authentic IPs in the CE and computing systems [31]-[41].

#### 1.3.2. Fraudulent Ownership Claim of IP Core

A deceitful IP buyer or an adversary (may present in foundry) present in the IC supply chain may fraudulently claim the IP ownership. This may lead huge

financial loss for the original IP owner. Therefore, false claim of ownership is a surging security concern. The standard IP protection mechanisms such as copyright, patent, trademark, industrial design rights etc. are not applicable for reusable IP cores designs. Therefore, it is crucial to ensure the protection of ownership rights of actual owner. In such scenarios, implanting designers' signature secretly in the IP core during its design process can be useful for proving the ownership right of an IP vendor and nullifying the fraudulent IP ownership claim by an adversary [40], [41].

### 1.3.3. Reverse Engineering Attack