## HARDWARE (IP) SECURITY FOR DSP AND MULTIMEDIA APPLICATIONS

Ph.D. Thesis

## By **MAHENDRA RATHOR**

# DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE SEPTEMBER 2021

## HARDWARE (IP) SECURITY FOR DSP AND MULTIMEDIA APPLICATIONS

## **A THESIS**

Submitted in partial fulfillment of the requirements for the award of the degree

of DOCTOR OF PHILOSOPHY

by

MAHENDRA RATHOR

# DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE SEPTEMBER 2021

## INDIAN INSTITUTE OF TECHNOLOGY INDORE

## CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled HARDWARE (IP) SECURITY FOR DSP AND MULTIMEDIA APPLICATIONS in the partial fulfillment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY and submitted in the DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING, INDIAN INSTITUTE OF TECHNOLOGY INDORE, is an authentic record of my own work carried out during the time period from DECEMBER, 2018 to SEPTEMBER 2021 under the supervision of Dr. ANIRBAN SENGUPTA, Associate Professor, Indian Institute of Technology, Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

| Signature of the student with date |

|------------------------------------|

| (MAHENDRA RATHOR)                  |

| <br>                               |

This is to certify that the above statement made by the candidate is correct to the best of my/our knowledge.

Signature of Thesis Supervisor with date (ANIRBAN SENGUPTA)

MAHENDRA RATHOR has successfully given his/her Ph.D. Oral Examination held on

| Signature of Chairperson (OEB) Date: | Signature of External Examiner Date:  | Signature(s) of Thesis Supervisor(s) Date: |

|--------------------------------------|---------------------------------------|--------------------------------------------|

| Signature of PSPC Member #1 Date:    | Signature of PSPC Member #2 Date:     | Signature of PSPC Member #3 Date:          |

| Signature of Convener, DPGC Date:    | Signature of Head of Discipline Date: |                                            |

## **ACKNOWLEDGEMENTS**

First and foremost, I wish to express my sincere gratitude to my supervisor Dr. Anirban Sengupta for providing me the opportunity to do work under their supervision. I wish to thank them for their persistence and faith in me, without their relentless effort and guidance I would have not been to understand the importance of research and the sacrifice it requires to reach a certain level. I have learned a lot from their invaluable advice, kindness, profoundness and experience. Under their supervision, I transformed into a person with more values.

I also owe a mention to Dr. Abhishek Srivastava, Dr. Manish Goyal and Dr. Puneet Gupta for their valuable feedbacks on my research work throughout these years.

Further, I wish to express my deepest gratitude to my parents, for their strong belief in me and for their continuous support all the way. I also wish to express my gratitude to my dear wife, Lakshmi, for being the driving force of my career and for her moral and emotional support throughout the PhD work. Thank you for being with me every single moment to keep me always prepared to work for the past three years.

I wish to thank all the faculty members and colleagues for their continuous support. The time spent at IIT Indore will always remain the most valuable memory of my life.

At last, I wish to thank IIT Indore, DST and CSIR to help financially and providing me an opportunity to present my research at international grounds.

## DEDICATED TO MY FATHER LATE SHRI MOHANLAL RATHOR

## **ABSTRACT**

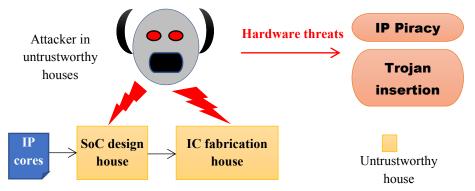

A core based design paradigm has become popular in the semiconductor business market for the last few decades. The underlying reasons are the increasing time to market pressure, design complexity and cost of system-on-chip (SoC) designs. However, the contrast impact of core based design paradigm is the susceptibility of the intellectual property (IP) cores towards the hardware threats of IP piracy and hardware Trojan insertion. An adversary in the untrusted SoC design house may infringe or misuse the IP core for personal benefits. Moreover, the reliance of chip manufacturing on a distinct offshore foundry also enhances the risks of IP piracy and potential Trojan insertion.

The digital signal processing (DSP) and multimedia applications are thriving in the modern consumer electronics (CE) market. The stringent performance and low power demand have enforced the realization of DSP and multimedia applications through their hardware accelerator or application specific IPs. However, owing to the proliferating usage of DSP and multimedia IPs in the SoCs, their security concerns cannot be undervalued. Hence, an IP core designer needs to employ protection measures against the piracy and potential Trojan insertion attacks to ensure trust in hardware. For highly complex designs such as DSP and multimedia cores, a high level synthesis (HLS) framework is amenable to employing security mechanisms. Towards the security of IP cores, this thesis contributes the following novel methodologies: (a) IP core steganography approaches to secure DSP cores against piracy, (b) a hologram based obfuscation approach to thwart the potential Trojan insertion attack, (c) double line of defense approaches based on structural obfuscation and IP vendor's secret mark to counter both Trojan insertion and IP piracy attacks, (d) secured hardware accelerator design approach for various image processing filter applications and a DFT processor.

### LIST OF PUBLICATIONS

## PEER-REVIEWED JOURNALS (12):

- A. Sengupta and M. Rathor, "Protecting DSP Kernels using Robust Hologram based obfuscation", *IEEE Transactions on Consumer Electronics*, vol. 65, no. 1, Feb 2019, pp. 99-108, Impact Factor: 2.947.

- 2. A. Sengupta and M. Rathor, "IP Core Steganography for Protecting DSP Kernels used in CE Systems," *IEEE Transactions on Consumer Electronics*, vol. 65, no. 4, Nov. 2019, pp. 506 515, **Impact Factor: 2.947**.

- M. Rathor and A. Sengupta, "IP Core Steganography Using Switch Based Key-Driven Hash-Chaining and Encoding for Securing DSP Kernels Used in CE Systems," *IEEE Transactions on Consumer Electronics*, vol. 66, no. 3, pp. 251-260, Aug. 2020, Impact Factor: 2.947.

- A. Sengupta and M. Rathor, "Enhanced Security of DSP Circuits Using Multi-Key Based Structural Obfuscation and Physical-Level Watermarking for Consumer Electronics Systems", *IEEE Transactions on Consumer Electronics*, vol. 66, no. 2, May 2020, pp. 163-172, Impact Factor: 2.947.

- A. Sengupta and M. Rathor, "Obfuscated Hardware Accelerators for Image Processing Filters-Application Specific and Functionally Reconfigurable Processors," *IEEE Transactions on Consumer Electronics*, vol. 66, no. 4, pp. 386-395, Nov. 2020, Impact Factor: 2.947.

- 6. A. Sengupta and M. Rathor, "Security of Functionally Obfuscated DSP core against Removal Attack using SHA-512 based Key Encryption Hardware", *IEEE Access Journal*, vol. 7, pp. 4598-4610, 2019, **Impact Factor: 3.367**.

- 7. M. Rathor and A. Sengupta, "Robust Logic locking for Securing Reusable DSP Cores," *IEEE Access*, vol. 7, pp. 120052-120064, 2019, **Impact Factor: 3.367**.

- 8. A. Sengupta and M. Rathor, "Structural Obfuscation and Crypto-Steganography based Secured JPEG Compression Hardware for Medical Imaging Systems", *IEEE Access*, vol. 8, pp. 6543-6565, 2020, **Impact Factor: 3.367**.

- M. Rathor and A. Sengupta, "Low-Cost Robust Anti-Removal Logic for Protecting Functionally Obfuscated DSP core against Removal Attack", *IET Electronics Letters*, vol. 55, no. 7, pp. 374-376, 2019, Impact Factor: 1.1316.

- A. Sengupta and M. Rathor, "Crypto based Dual phase Hardware Steganography for Securing IP cores," *IEEE Letters of the Computer Society*, vol. 2, no. 4, pp. 32-35, 2019.

- 11. M. Rathor and A. Sengupta, "Design Flow of Secured N-Point DFT Application Specific Processor Using Obfuscation and Steganography," *IEEE Letters of the Computer Society*, vol. 3, no. 1, pp. 13-16, 2020.

- 12. A. Sengupta, M. Rathor, S Patil, and NG Harishchandra, "Securing Hardware Accelerators Using Multi-Key Based Structural Obfuscation," *IEEE Letters of the Computer Society*, vol. 3, no. 1, pp. 21-24, 2020.

#### BOOK CHAPTERS (6):

- A. Sengupta and M. Rathor, "Designing Secured N-point DFT Hardware Accelerator using Obfuscation and Steganography", *IET Book: Secured Hardware Accelerators for DSP and Image processing applications*, 2021, Print: 978-1-83953-306-8, eBook: 978-1-83953-307-5.

- A. Sengupta and M. Rathor, "Structural transformation and obfuscation frameworks for Data-intensive IPs", *IET Book: Secured Hardware Accelerators for DSP and Image processing applications*, 2021, Print: 978-1-83953-306-8, eBook: 978-1-83953-307-5.

- 15. A. Sengupta and M. Rathor, "Security of Functionally Obfuscated DSP cores", *IET Book: Frontiers in Securing Hardware IP Cores: Forensic detective control and obfuscation techniques*, 2020, ISBN: 978-1-83953-031-9/978-1-83953-032-6.

- A. Sengupta and M. Rathor, "Hologram based Structural Obfuscation for DSP Cores", *IET Book: Frontiers in Securing Hardware IP Cores: Forensic detective* control and obfuscation techniques, 2020, ISBN: 978-1-83953-031-9/978-1-83953-032-6.

- 17. A. Sengupta and M. Rathor, "Hardware (IP) Watermarking during Behavioural Synthesis", *Springer Book: Behavioral Synthesis for Hardware Security*, 2020, Invited Chapter (Eds.Srinivas Katkoori, Sheikh Ariful Islam).

- 18. A. Sengupta and M. Rathor, "Design Space Exploration of DSP hardware using Bacterial Foraging and Particle Swarm Optimization Algorithm for Power/Area-Delay Tradeoff", *IET Book: Low Power Nanoscale IC Design*, Invited Book Chapter, 2020, Print ISBN: 978-981-15-7936-3.

#### PEER- REVIEWED CONFERENCE PUBLICATIONS (4):

- M. Rathor, P. Sarkar, VK Mishra and A. Sengupta, "Securing IP Cores in CE Systems using Key-driven Hash-chaining based Steganography", *Proceedings of* 10th IEEE International Conference on Consumer Electronics- Berlin (ICCE Berlin), Germany, 2020, pp. 1-4.

- M. Rathor and A. Sengupta, "Obfuscating DSP Hardware Accelerators in CE Systems Using Pseudo Operations Mixing", Proceedings of 4th IEEE International Conference on Zooming Innovation in Consumer Electronics 2020 (ZINC 2020), Serbia, 2020, pp. 218-221.

- 21. M. Rathor and A. Sengupta, "Enhanced Functional Obfuscation of DSP core using Flip-Flops and Combinational logic", *Proceedings of 9th IEEE International Conference on Consumer Electronics (ICCE)- Berlin*, Berlin, 2019, pp. 1-5.

- 22. A. Sengupta and M. Rathor, "Improved Delay Estimation Model for Loop Based DSP Cores", *Proceedings of 37th IEEE International Conference on Consumer Electronics (ICCE)*, Las Vegas, USA, Jan 2019, pp. 1-4.

## TABLE OF CONTENTS

|    | ABSTRA            |                                                                           | VI  |

|----|-------------------|---------------------------------------------------------------------------|-----|

|    |                   | PUBLICATIONS                                                              | VII |

|    |                   | FIGURES                                                                   | XII |

|    |                   | TABLES                                                                    | XVI |

|    |                   | ICLATURE                                                                  | XIX |

|    | ACRON             | YMS                                                                       | XXI |

| 1. | Chapter           | 1                                                                         | 1   |

|    | Introduct         | tion                                                                      |     |

|    | 1.1               | Semiconductor IP core and its various forms                               | 3   |

|    | 1.2               | DSP and multimedia applications and corresponding                         | 3   |

|    |                   | algorithmic representation                                                |     |

|    | 1.3               | Threats to IP cores                                                       | 4   |

|    | 1.4               | Background on high level synthesis and its importance in IP core security | 7   |

|    | 1.5               | Organization of thesis                                                    | 10  |

| 2. | Chapter 2         | 2                                                                         | 11  |

|    | State of t        | the art                                                                   |     |

|    | 2.1               | State of the art on handling IP piracy threat                             | 11  |

|    | 2.2               | State of the art on thwarting hardware Trojan insertion attack            | 15  |

|    | 2.3               | Objective of the thesis                                                   | 17  |

|    | 2.4               | Summary of the contributions                                              | 18  |

|    |                   | -                                                                         |     |

| 3. | Chapter           | 3                                                                         | 21  |

|    | Hardwar<br>piracy | re steganography techniques for securing IP cores against                 |     |

|    | 3.1               | Problem formulation                                                       | 22  |

|    | 3.2               | Entropy based hardware steganography                                      | 22  |

|    | 3.3               | Key-driven hash chaining based IP core steganography                      | 30  |

|    | 3.4               | Metric for evaluating impact of proposed steganography                    | 40  |

|    | 3.5               | techniques on design cost<br>Summary                                      | 41  |

| 4  | Chapter           | 4                                                                         | 42  |

|    | Hologran          | m based structural obfuscation to thwart reverse                          |     |

engineering based attacks

|   | 4.1                | Problem formulation                                                                                              | 43 |

|---|--------------------|------------------------------------------------------------------------------------------------------------------|----|

|   | 4.2                | Hologram based structural obfuscation approach                                                                   | 43 |

|   | 4.3                | Demonstration on generating hologram obfuscated FIR-IIR filter integrated datapath                               | 47 |

|   | 4.4                | Similarity of hologram obfuscated design with a security image hologram                                          | 50 |

|   | 4.5                | Summary                                                                                                          | 51 |

| 5 | Chapter            | 5                                                                                                                | 52 |

|   |                    | ine of defense approach using integrated structural ion and crypto-steganography to secure IP cores              |    |

|   | 5.1                | Problem formulation                                                                                              | 52 |

|   | 5.2                | The double line of defense during high level synthesis process for securing IP cores                             | 52 |

|   | 5.3                | Demonstration of securing application specific processors using double line of defense                           | 60 |

|   | 5.4                | Summary                                                                                                          | 66 |

| 6 | Chapter            | 6                                                                                                                | 67 |

|   |                    | ine of defense approach using integrated multi-key based l obfuscation and physical level watermarking to secure |    |

|   | 6.1                | Problem formulation                                                                                              | 67 |

|   | 6.2                | The double line of defense during high level and physical synthesis processes for securing IP cores              | 67 |

|   | 6.3                | Demonstration of securing IP cores using double line of defense                                                  | 73 |

|   | 6.4                | Summary                                                                                                          | 77 |

| 7 | Chapter            | 7                                                                                                                | 78 |

|   | Secured processing | hardware accelerator design approach for image ng filters                                                        |    |

|   | 7.1                | Problem formulation                                                                                              | 79 |

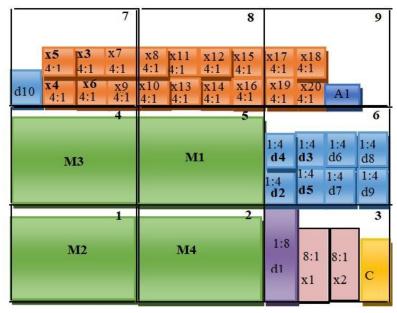

|   | 7.2                | Design approach of a secured 3x3 filter hardware accelerator                                                     | 80 |

|   | 7.3                | Design approach of a secured 5x5 filter hardware accelerator                                                     | 90 |

|   | 7.4                | Summary                                                                                                          | 93 |

| 8 | Chapter            | 8                                                                                                                | 94 |

|   | -                  | ues for securing functionally obfuscated DSP cores emoval attack                                                 |    |

|    | 8.1      | Problem formulation                                                                                                                                              | 95  |

|----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 8.2      | Overview of ILB and its features                                                                                                                                 | 95  |

|    | 8.3      | SHA-512 based ILB-keys generation hardware to secure against removal attack                                                                                      | 96  |

|    | 8.4      | Anti-removal logic (ARL) unit to secure against removal attack                                                                                                   | 102 |

|    | 8.5      | Summary                                                                                                                                                          | 106 |

| 9  | Chapter  | 9                                                                                                                                                                | 107 |

|    | Robust l | logic locking technique for preventing IP piracy                                                                                                                 |     |

|    | 9.1      | Problem formulation                                                                                                                                              | 107 |

|    | 9.2      | Logic locking technique for securing DSP cores against IP piracy                                                                                                 | 107 |

|    | 9.3      | Addressing different Attacks Scenarios                                                                                                                           | 116 |

|    | 9.4      | Summary                                                                                                                                                          | 118 |

| 10 | Chapter  | 10                                                                                                                                                               | 119 |

|    | Experim  | nental results and analysis                                                                                                                                      |     |

|    | 10.1     | Results and analysis: Hardware steganography techniques for securing IP cores against piracy                                                                     | 119 |

|    | 10.2     | Results and analysis: Hologram based structural obfuscation to thwart reverse engineering based attacks                                                          | 124 |

|    | 10.3     | Results and analysis: Double line of defense approach using integrated structural obfuscation and cryptosteganography to secure IP cores                         | 126 |

|    | 10.4     | Results and analysis: Double line of defense approach using integrated multi-key based structural obfuscation and physical level watermarking to secure IP cores | 129 |

|    | 10.5     | Results and analysis: Secured hardware accelerator design approach for image processing filters                                                                  | 132 |

|    | 10.6     | Results and analysis: Techniques for securing functionally obfuscated DSP cores against removal attack                                                           | 134 |

|    | 10.7     | Results and analysis: Robust logic locking technique for preventing IP piracy                                                                                    | 138 |

| 11 | Chapter  | 11                                                                                                                                                               | 141 |

|    | Conclus  | ion and future work                                                                                                                                              |     |

|    | 11.1     | Conclusion                                                                                                                                                       | 141 |

|    | 11.2     | Future work                                                                                                                                                      | 143 |

|    | REFER    | ENCES                                                                                                                                                            | 144 |

## LIST OF FIGURES

| Figure 1.1  | Potential hardware security threats in untrustworthy houses                                                                                                     | 5  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

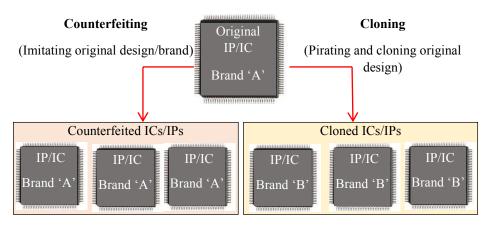

| Figure 1.2  | Counterfeiting and cloning attacks, where brand 'A' indicates the brand name of a genuine IP vendor and brand 'B' indicates the brand name used by an adversary | 6  |

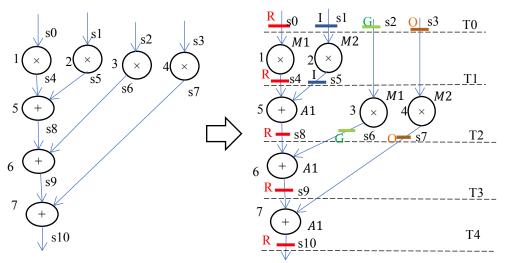

| Figure 1.3  | (a) DFG of 4-point DCT (b) Scheduled and hardware allocated 4point DCT using resource constraints of 1 (+) and $2(\times)$                                      | 9  |

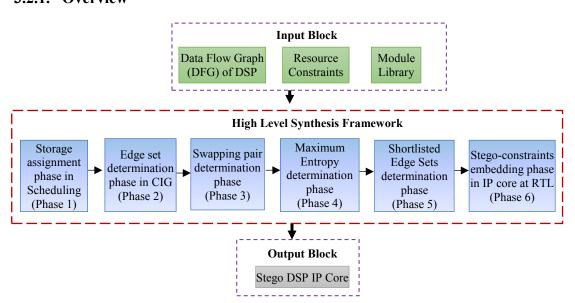

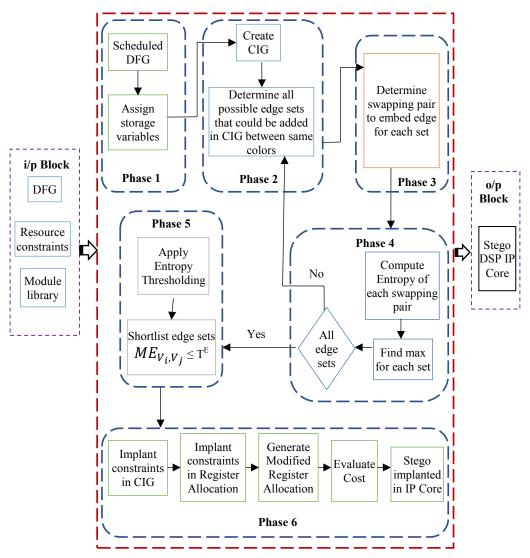

| Figure 3.1  | Overview of the implanting hardware steganography in IP cores                                                                                                   | 22 |

| Figure 3.2  | Embedding process of hardware steganography for an IP Core                                                                                                      | 23 |

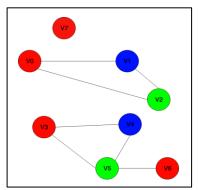

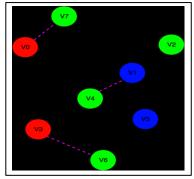

| Figure 3.3  | CIG of the sample application                                                                                                                                   | 24 |

| Figure 3.4  | Final CIG after implanting all the edges                                                                                                                        | 26 |

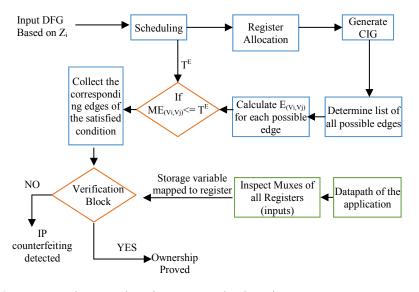

| Figure 3.5  | Proposed entropy based steganography detection process                                                                                                          | 27 |

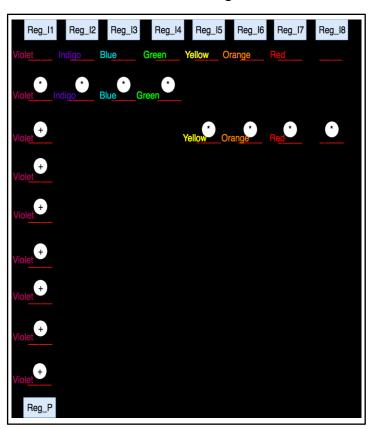

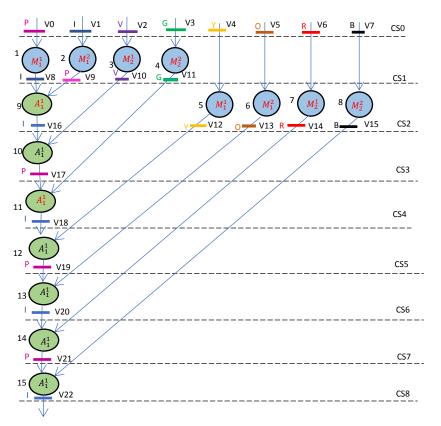

| Figure 3.6  | Scheduled and hardware allocated 8-point DCT using 1 (+) and 4 (×)                                                                                              | 28 |

| Figure 3.7  | The stego-embedded scheduled and hardware allocated 8-point DCT                                                                                                 | 29 |

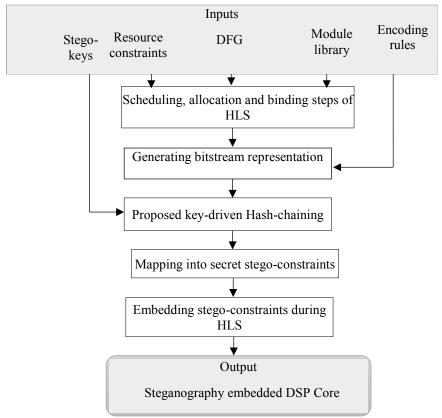

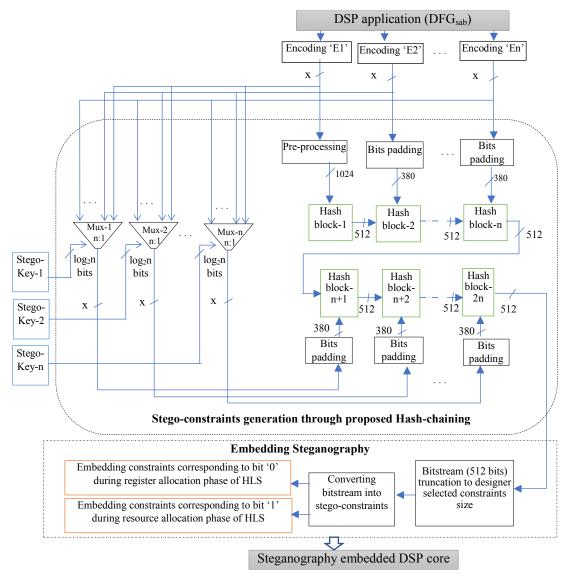

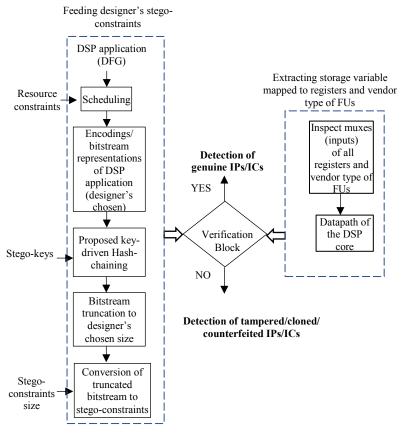

| Figure 3.8  | Overview of key-driven hash-chaining based steganography                                                                                                        | 31 |

| Figure 3.9  | Details of proposed key-driven hash-chaining based steganography                                                                                                | 32 |

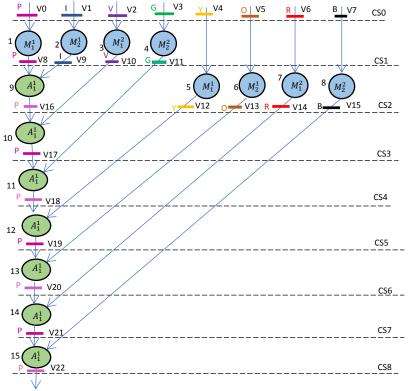

| Figure 3.10 | DFG <sub>sab</sub> of 8-point DCT using 1 A and 4 M before implanting steganography                                                                             | 33 |

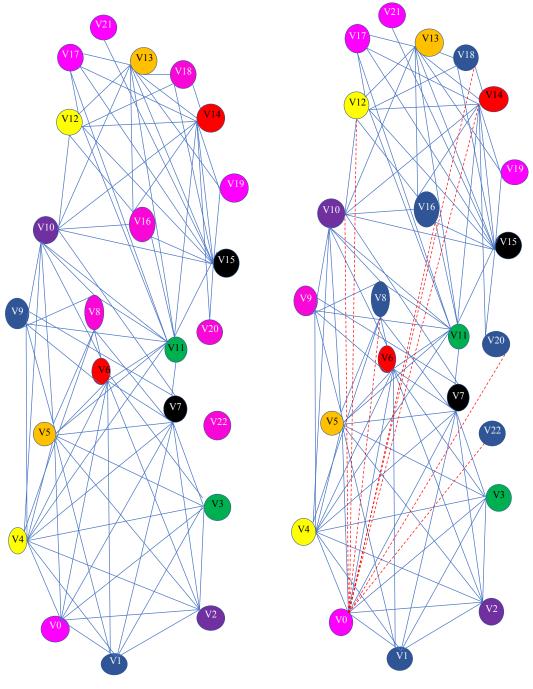

| Figure 3.11 | (a) CIG of 8-point DCT before steganography (b) CIG of 8-point DCT after steganography                                                                          | 35 |

| Figure 3.12 | Scheduled and hardware allocated 8-point DCT after implanting steganography                                                                                     | 37 |

| Figure 3.13 | Detection process of key-driven hash chaining based steganography                                                                                               | 38 |

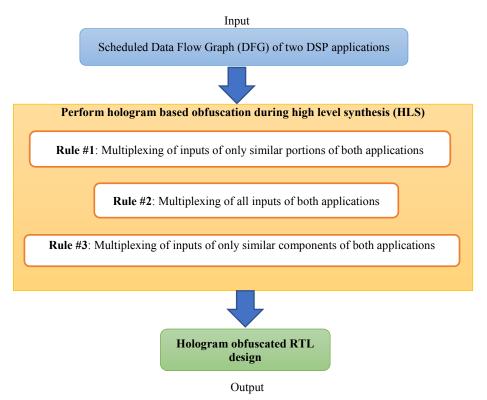

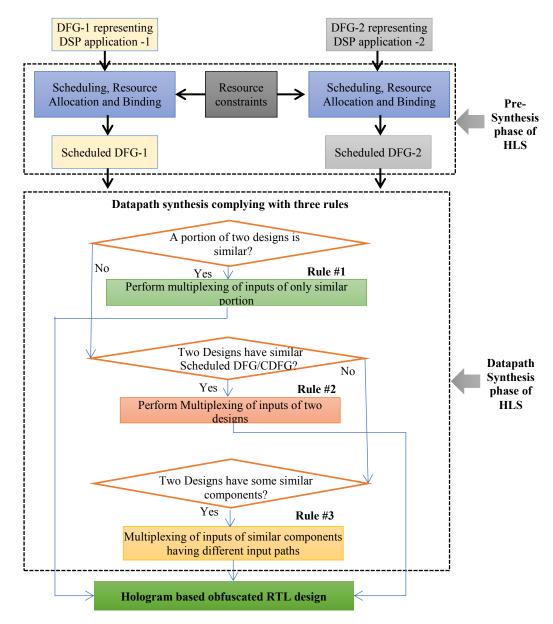

| Figure 4.1  | Overview of Hologram based obfuscation approach                                                                                                                 | 43 |

| Figure 4.2  | Flow of generating a Hologram obfuscated DSP design                                                                                                             | 45 |

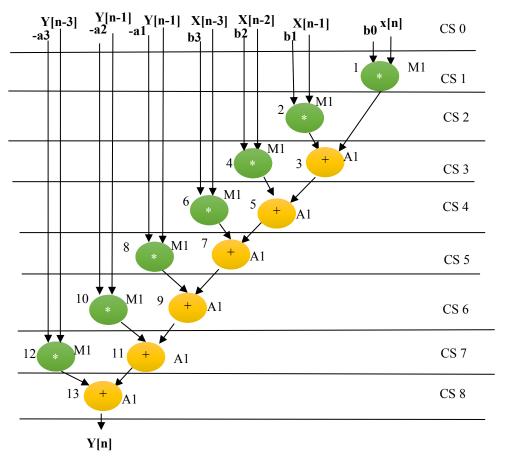

| Figure 4.3 | Scheduling of IIR filter based on 1 adder and 1 multiplier                                                                                                     | 48 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

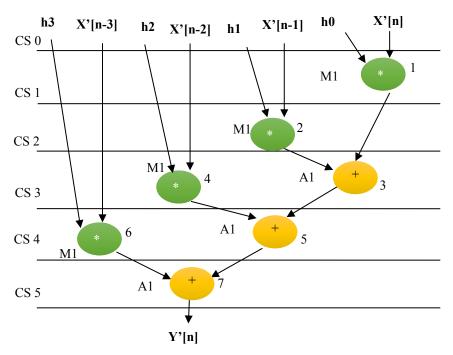

| Figure 4.4 | Scheduled DFG of FIR filter based on 1 adder and 1 multiplier                                                                                                  | 49 |

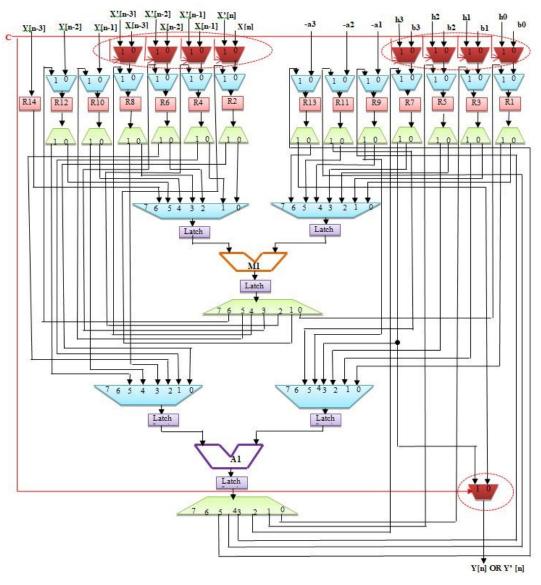

| Figure 4.5 | Hologram based structurally obfuscated integrated RTL design of IIR and FIR filter cores                                                                       | 50 |

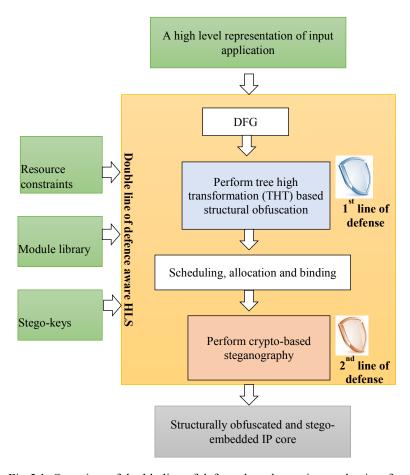

| Figure 5.1 | Overview of double line of defense based security mechanism for securing IP cores                                                                              | 53 |

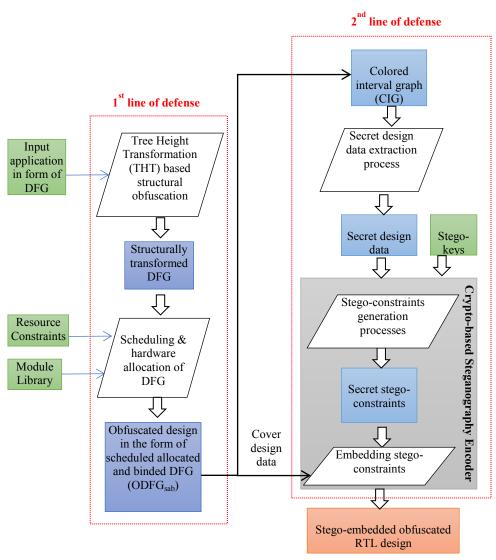

| Figure 5.2 | Flow of the process of securing JPEG codec processor using structural obfuscation (first line of defense) and crypto-based steganography (second line defense) | 54 |

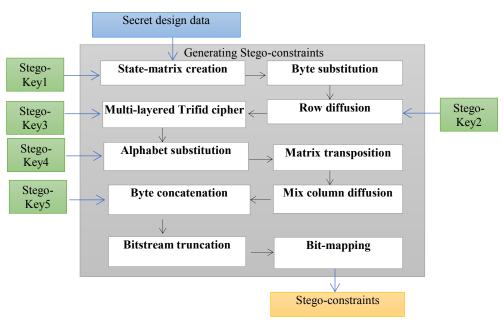

| Figure 5.3 | Steps of stego-constraints generation process of crypto-<br>based steganography encoder system                                                                 | 55 |

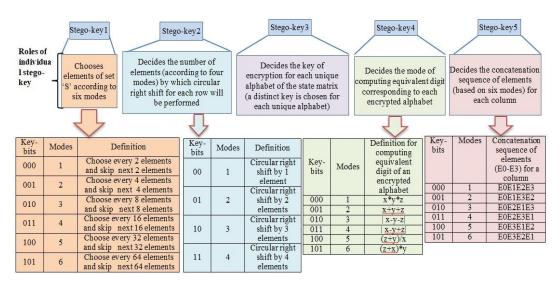

| Figure 5.4 | Roles and various modes of stego-key1 to stego-key5                                                                                                            | 56 |

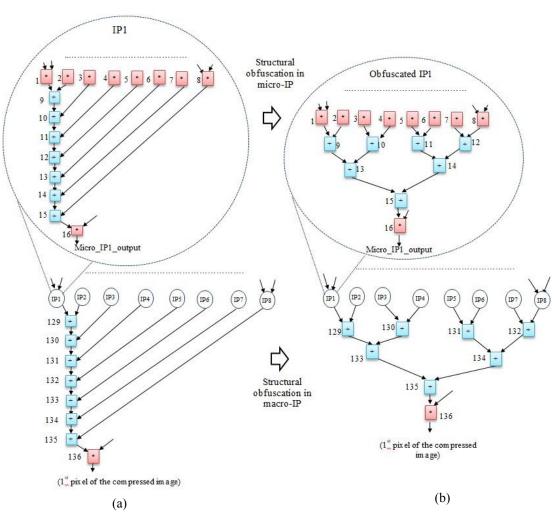

| Figure 5.5 | (a) DFG of JPEG compression application (b) THT based obfuscated DFG                                                                                           | 61 |

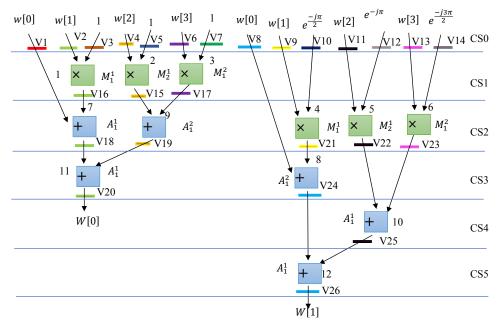

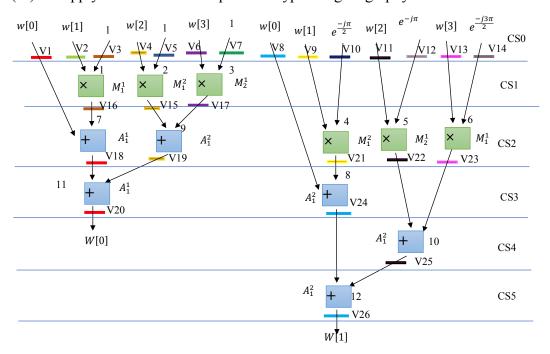

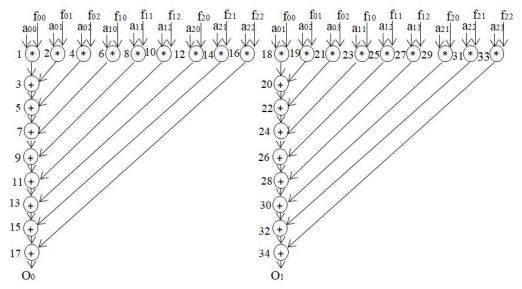

| Figure 5.6 | $ODFG_{sab}$ of obfuscated 4-point DFT based on 3M and 2A                                                                                                      | 63 |

| Figure 5.7 | ODFG <sub>sab</sub> of 4-point DFT post embedding stego-information                                                                                            | 64 |

| Figure 5.8 | Secured 4-point DFT processor at RTL                                                                                                                           | 65 |

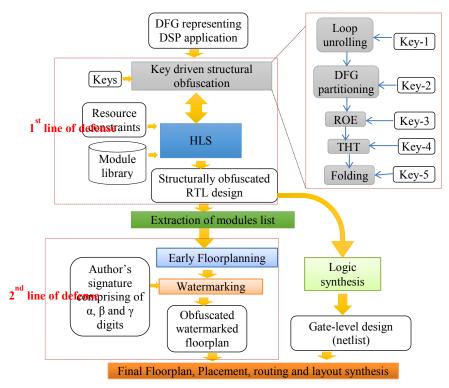

| Figure 6.1 | The flow of proposed key-driven structural obfuscation<br>and physical level watermarking based double line of<br>defense                                      | 68 |

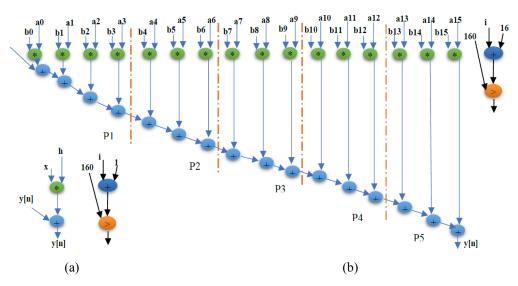

| Figure 6.2 | (a) DFG representing 160-tap FIR filter (b) loop unrolled FIR filter with UF=16                                                                                | 74 |

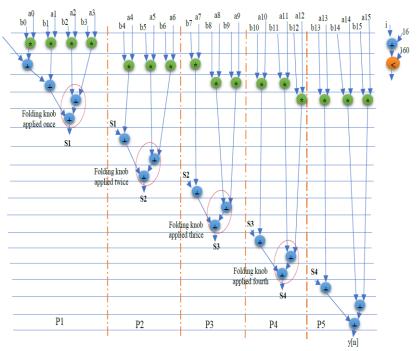

| Figure 6.3 | Post applying THT based obfuscation in all partitions                                                                                                          | 74 |

| Figure 6.4 | Obfuscated scheduled FIR filter with applied folding at                                                                                                        | 75 |

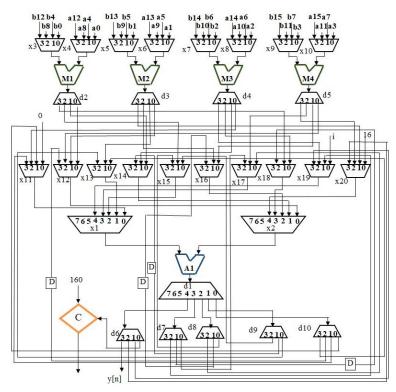

| Figure 6.5 | 4 instances Key-driven structurally obfuscated RTL datapath of FIR filter                                                                                      | 75 |

| Figure 6.6 | Early floorplan of obfuscated FIR filter                                                                                                                       | 76 |

| Figure 6.7 | Watermarked floorplan of obfuscated FIR filter                                                                                                                 | 76 |

| Figure 7.1 | Generating filtered image using secured hardware accelerator of image processing filters                                                                       | 79 |

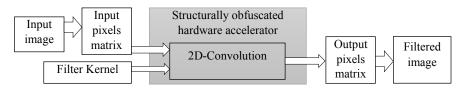

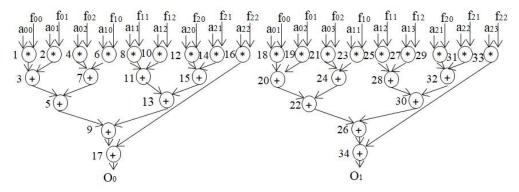

| Figure 7.2 | Loop unrolled DFG of 3×3 image filter application                                                                                                              | 82 |

| Figure 7.3 | THT obfuscated loop unrolled DFG of 3×3 image filter application                                                                                               | 82 |

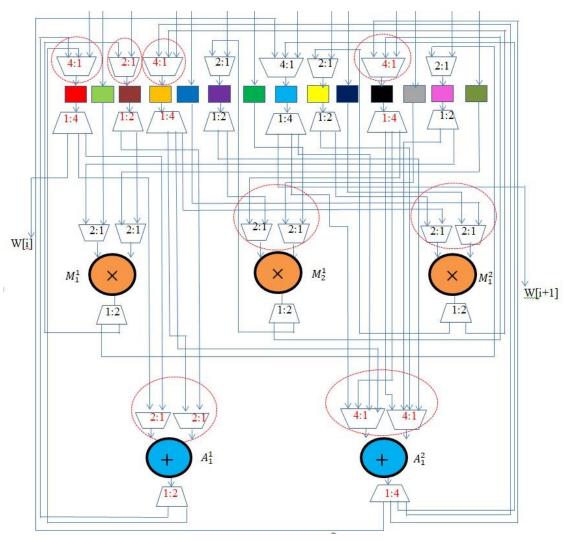

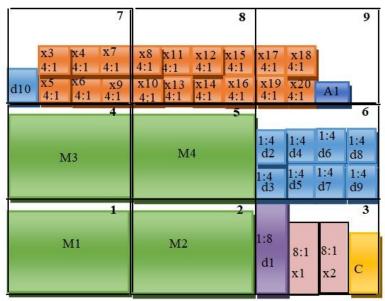

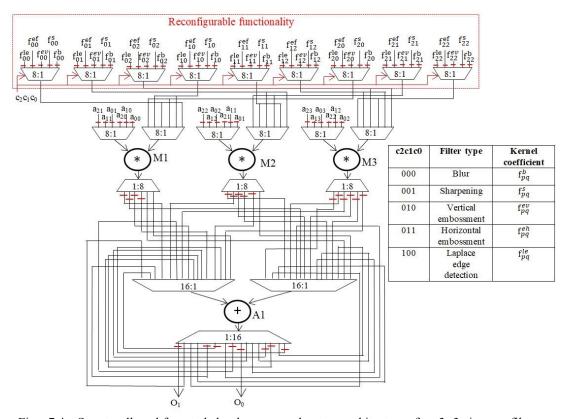

| Figure 7.4  | Structurally obfuscated hardware accelerator architecture for 3×3 image filter applications with reconfigurable functionality       | 83  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

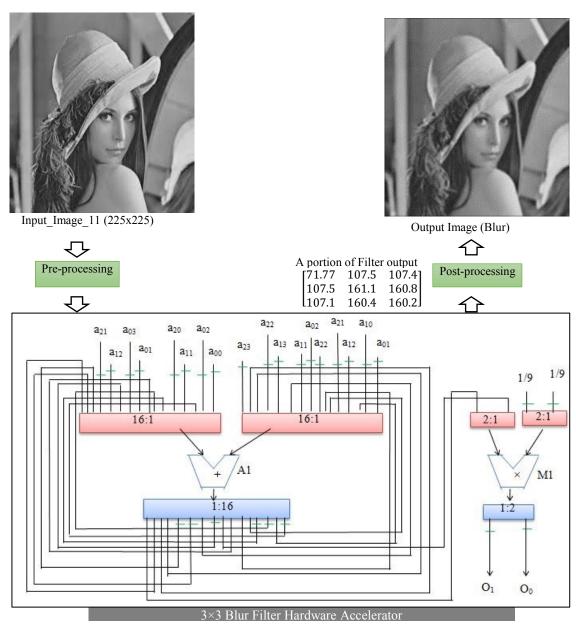

| Figure 7.5  | End to end demonstration of image blurring application using 3x3 blur filter                                                        | 85  |

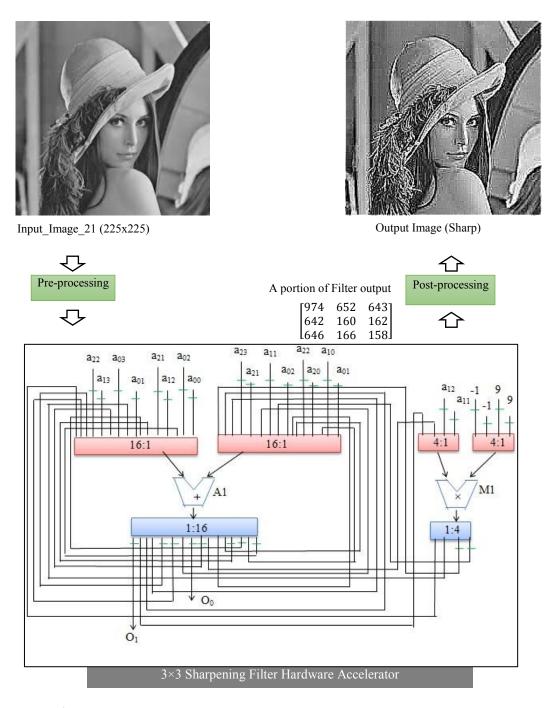

| Figure 7.6  | End to end demonstration of image sharpening application using a 3x3 filter                                                         | 86  |

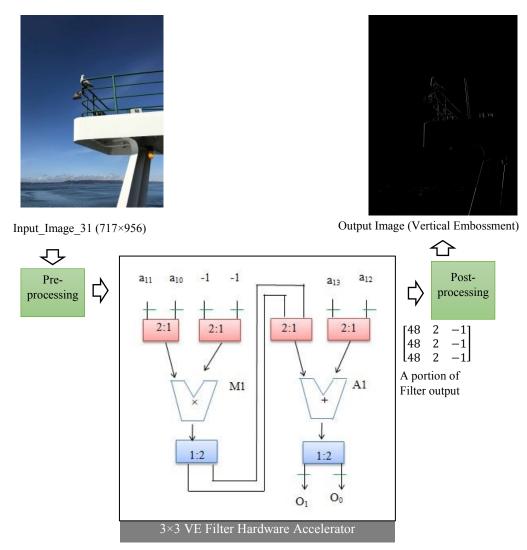

| Figure 7.7  | End to end demonstration of vertical embossment application using 3x3 filter                                                        | 87  |

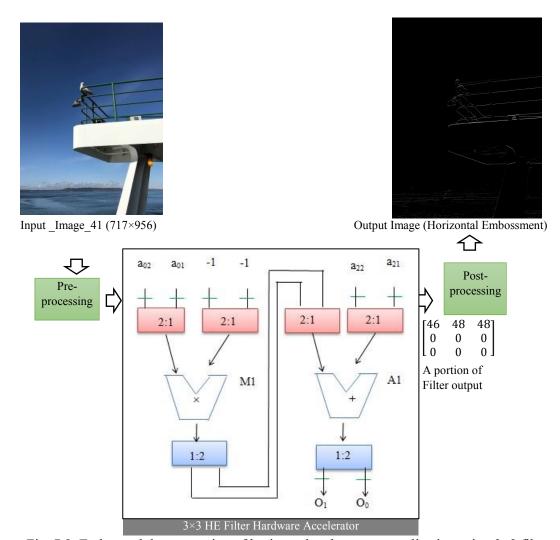

| Figure 7.8  | End to end demonstration of horizontal embossment application using 3×3 filter                                                      | 89  |

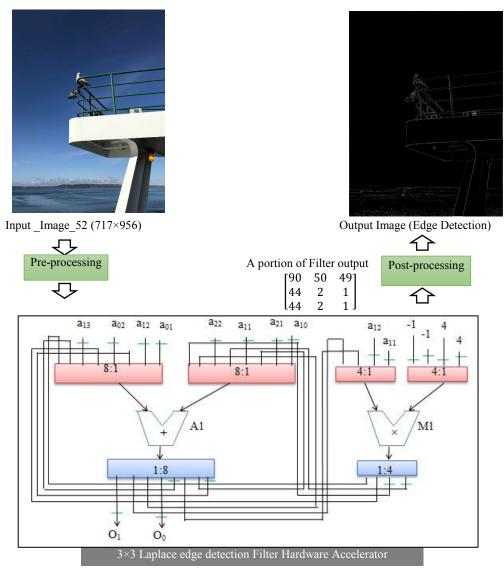

| Figure 7.9  | End to end demonstration of edge detection using 3×3 edge detection filter                                                          | 90  |

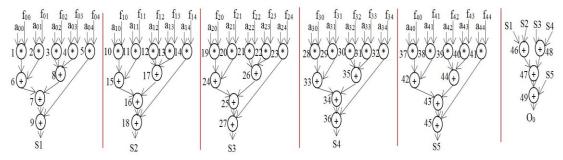

| Figure 7.10 | Partitioned DFG of 5×5 filter application post performing THT based structural obfuscation                                          | 92  |

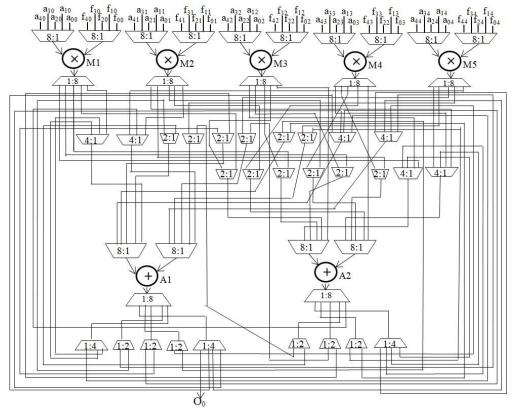

| Figure 7.11 | Structurally obfuscated RTL datapath of 5×5 image filter hardware accelerator                                                       | 92  |

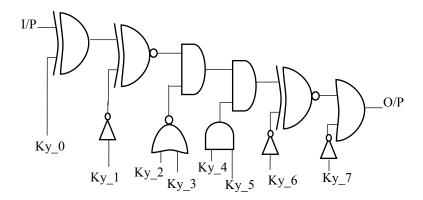

| Figure 8.1  | A sample ILB structure requiring an 8-bit key 'k1' to activate                                                                      | 95  |

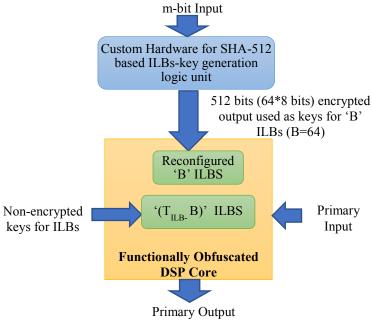

| Figure 8.2  | Overview of securing a functionally obfuscated DSP core against the removal attack using SHA-512 based ILBs-key generation hardware | 96  |

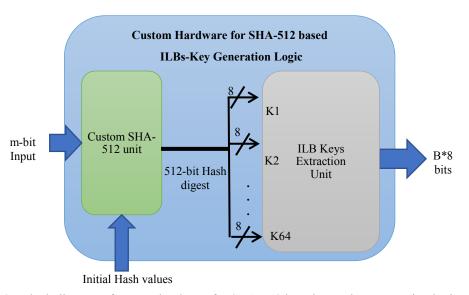

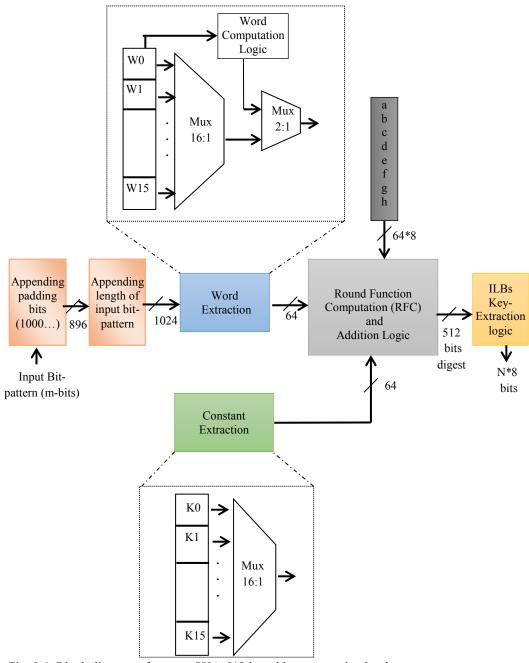

| Figure 8.3  | Block diagram of custom hardware for SHA-512 based ILBs-key generation logic                                                        | 97  |

| Figure 8.4  | Block diagram of custom SHA-512 based key generation hardware                                                                       | 99  |

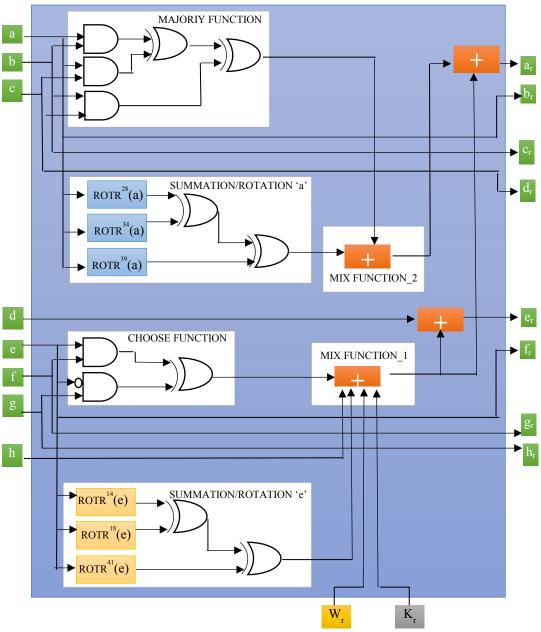

| Figure 8.5  | Round Function Computation hardware of custom SHA-512                                                                               | 100 |

| Figure 8.6  | Example of a configured ILBy based on the output "10110000" produced from ILB key selection logic                                   | 102 |

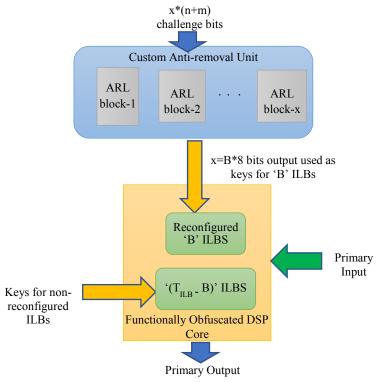

| Figure 8.7  | Overview of using ARL unit to protect a functionally obfuscated DSP core against the removal attack                                 | 103 |

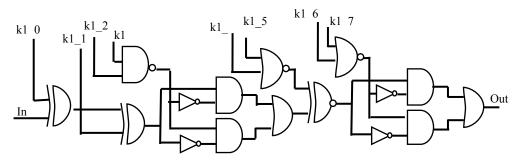

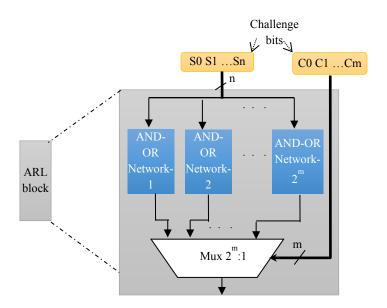

| Figure 8.8  | Overview of ARL block                                                                                                               | 105 |

| Figure 8.9  | Overview of an AND-OR network used in ARL block                                                                                     | 105 |

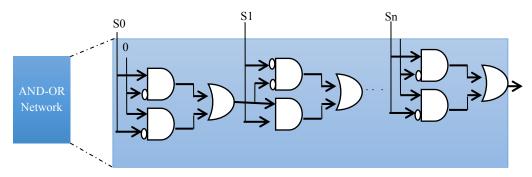

| Figure 9.1  | Overview of proposed logic locking methodology for DSP IP cores                                                                     | 108 |

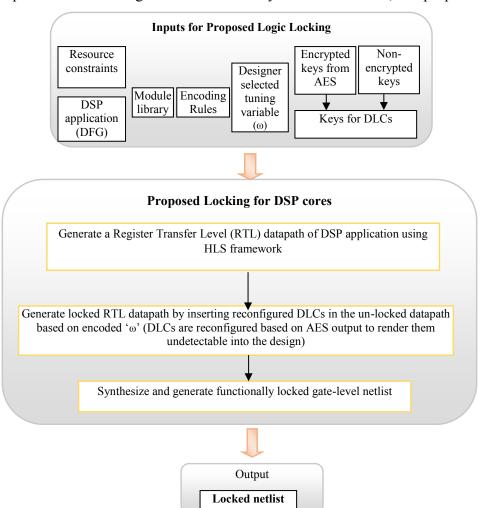

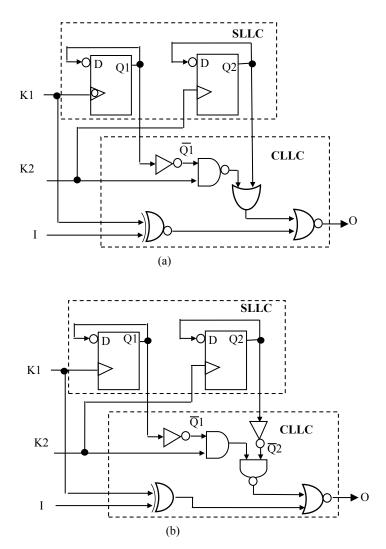

| Figure 9.2  | Proposed sample reconfigured DLC structures (where, "K1K2" is a two-bit key)                                                        | 110 |

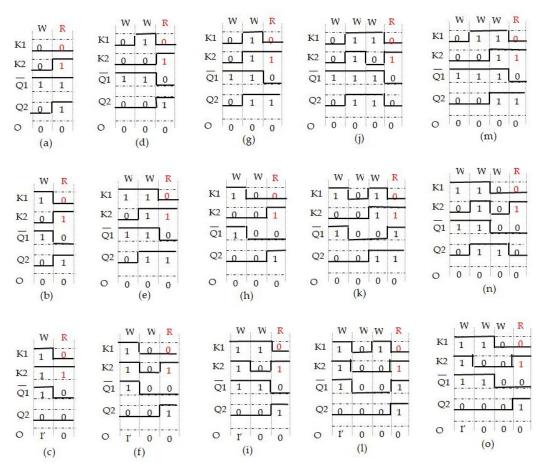

| Figure 9.3  | Waveforms showing that correct output is not obtained unless the correct key is applied only in the first trial                     | 111 |

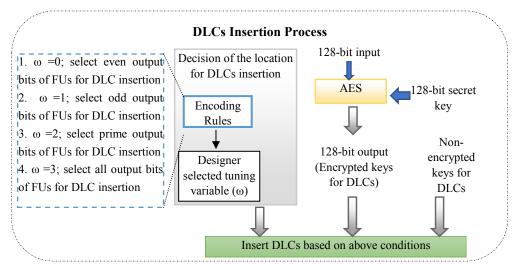

| Figure 9.4  | The process of DLCs insertion into RTL datapath of DSP cores                                                                                       | 114 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

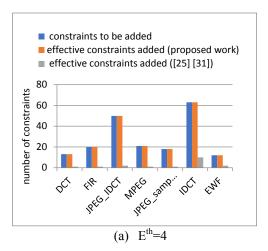

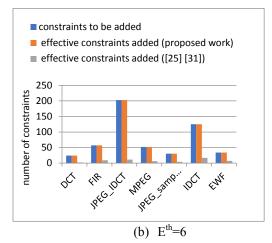

| Figure 10.1 | Estimation of the number of effective constraints added for both solutions (considering same number of constraints) at different entropy threshold | 120 |

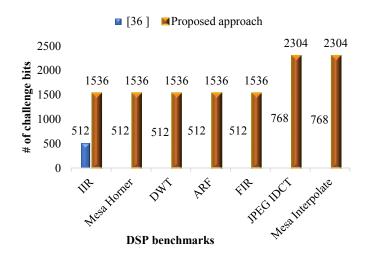

| Figure 10.2 | Security comparison of proposed work with [36]                                                                                                     | 137 |

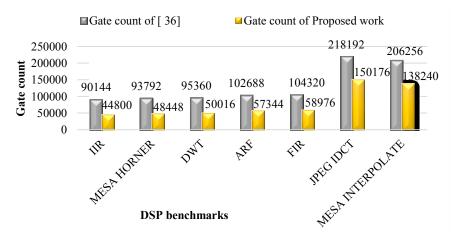

| Figure 10.3 | Gate count comparison of proposed work with [36]                                                                                                   | 137 |

## LIST OF TABLES

| Table 3.1   | Storage variable assignment of a sample application                                                                                                                                            | 24  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2   | Swapping pairs and corresponding entropies for the potential edges to be added                                                                                                                 | 25  |

| Table 3.3   | Storage assignment post implanting stego-constraints                                                                                                                                           | 26  |

| Table 6.1   | Roles and key-size of different keys used for proposed structural obfuscation                                                                                                                  | 69  |

| Table 10.1  | Impact on Pc using proposed IP steganography for different entropy threshold                                                                                                                   | 120 |

| Table 10.2  | Design cost of the proposed approach in terms of area and latency                                                                                                                              | 121 |

| Table 10.3  | Impact on storage overhead on increasing threshold entropy                                                                                                                                     | 121 |

| Table 10.4  | Comparison of proposed approach with [25], [31] in terms of the # of registers for the same # of constraints                                                                                   | 121 |

| Table 10.5  | Variation in Pc for increasing size of stego-constraints using proposed key-driven hash-chaining approach                                                                                      | 122 |

| Table 10.6  | Security of proposed approach in terms of maximum key size and attacker's total effort                                                                                                         | 123 |

| Table 10.7  | Impact of increasing size of stego-constraints on the design cost of proposed key driven hash chaining based steganography approach                                                            | 124 |

| Table 10.8  | Comparison of design cost of proposed approach with respect to baseline                                                                                                                        | 124 |

| Table 10.9  | Comparison of affected gate count between proposed obfuscation and baseline                                                                                                                    | 125 |

| Table 10.10 | Comparison of affected gate count between [45] and baseline                                                                                                                                    | 125 |

| Table 10.11 | Comparison of security of proposed obfuscation and [45]                                                                                                                                        | 125 |

| Table 10.12 | Comparison of JPEG compression hardware resources pre and post obfuscation                                                                                                                     | 127 |

| Table 10.13 | Security analysis in terms of strength of obfuscation for 4-point DFT processor                                                                                                                | 127 |

| Table 10.14 | Security analysis (in terms of Pc) of proposed crypto-<br>based steganography approach on varying size of<br>stego-constraints for different design solutions of JPEG<br>compression processor | 128 |

| Table 10.15 | Comparison of security of 4-point DFT in terms of Pc with the entropy based steganography approach                                                                         | 128 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 10.16 | Design cost analysis of proposed approach on varying size of stego-constraints for different design solutions of JPEG compression processor                                | 129 |

| Table 10.17 | Comparison of design cost of DFT processor with baseline and entropy based steganography                                                                                   | 129 |

| Table 10.18 | Strength of multi-key structural obfuscation in terms of gate count modified                                                                                               | 130 |

| Table 10.19 | Total key size for the proposed obfuscated watermarked design                                                                                                              | 130 |

| Table 10.20 | Security of proposed watermarking using probability of coincidence (Pc)                                                                                                    | 130 |

| Table 10.21 | Tamper tolerance and brute-force attack analysis of proposed obfuscated watermarked design                                                                                 | 131 |

| Table 10.22 | Design cost analysis of proposed approach                                                                                                                                  | 131 |

| Table 10.23 | RTL components of image processing filters of size 3x3 and 5x5                                                                                                             | 133 |

| Table 10.24 | Gate count of proposed filter hardware accelerators                                                                                                                        | 133 |

| Table 10.25 | Security analysis of proposed application specific image processing filters                                                                                                | 133 |

| Table 10.26 | Power and design cost of proposed application specific 3x3 filter hardware accelerators                                                                                    | 133 |

| Table 10.27 | Comparison of security in terms of key-bits encrypted for the ILBs of obfuscated design of proposed approach and [36]                                                      | 135 |

| Table 10.28 | Gate count comparison of baseline design with [36] and proposed methodology                                                                                                | 135 |

| Table 10.29 | Power comparison of baseline design, [36] and proposed work                                                                                                                | 135 |

| Table 10.30 | Comparison of design cost of proposed work with [36]                                                                                                                       | 136 |

| Table 10.31 | Comparison of the strength of the proposed logic locking with [36] [37] in terms of the probability of deducing correct key in exhaustive trials using eq. (9.3) and (9.4) | 139 |

| Table 10.32 | Attack time comparison of the proposed logic locking with [36] [37]                                                                                                        | 139 |

| Table 10.33 | Comparison of the encryption strength of the proposed logic locking with [36] [37]                                                                                         | 139 |

Table 10.34 Percent reduction in the resource count using proposed work w.r.t. [36] [37]

## **NOMENCLATURE**

| Vi                  | i <sup>th</sup> storage variable                                                  |

|---------------------|-----------------------------------------------------------------------------------|

| $E_{Vi,Vj}$         | Entropy of (Vi, Vj) storage variable pair                                         |

| ME <sub>Vi,Vj</sub> | Maximum entropy of (Vi, Vj) storage variable pair                                 |

| $T^{E}$             | Threshold entropy                                                                 |

| Pc                  | Probability of coincidence                                                        |

| G                   | Number of registers in the design                                                 |

| f                   | Number of stego-constraints embedded                                              |

| $F_b^a$             | b <sup>th</sup> instance of functional unit of vendor type a                      |

| $M_b^a$             | b <sup>th</sup> instance of multiplier of vendor type a                           |

| $A_b^a$             | b <sup>th</sup> instance of adder of vendor type a                                |

| DFG <sub>sab</sub>  | Scheduled, allocated and binded DFG                                               |

| N(Z <sub>i</sub> )  | Number of instances of functional unit Z of type i                                |

| key <sub>m</sub>    | Maximum possible size of the stego-key                                            |

| U                   | Total possible encodings for a DSP application                                    |

| A <sub>m</sub> sk   | Attacker's max effort in terms of deducing the stego-key                          |

| A <sub>m</sub> eb   | Attacker's effort in terms of finding the encoded bits                            |

| $A_T^S$             | Attacker's total effort in determining the stego-constraints                      |

| C <sub>f</sub> (Zi) | Cost of the design scheduled using the resource constraints Zi                    |

| $L_{T}$             | Design delay/latency                                                              |

| $A_{T}$             | Design area                                                                       |

| A <sub>max</sub>    | Maximum area                                                                      |

| L <sub>max</sub>    | Maximum delay                                                                     |

| $\beta_1, \beta_2$  | Weights assigned to latency and area in calculating the cost                      |

| $S_n$               | Strength of obfuscation                                                           |

| $G_c^f$             | Number of gates affected due to applying obfuscation                              |

| $G_c^T$             | Number of gates in the respective un-obfuscated design                            |

| $\Delta G_c^{fb}$   | Difference in gate count between obfuscated design and un-obfuscated version      |

| $G_c^{ip}$          | Number of gates altered in terms of input connectivity post obfuscation           |

| ODFG <sub>sab</sub> | Obfuscated scheduled, allocated and binded DFG                                    |

| u                   | Number of instances of FU type U <sub>r</sub> , where r is the total types of FUs |

| х                           | Number of Muxes of size $X_{\nu}$ , where $\nu$ indicates various sizes of Mux in the design      |

|-----------------------------|---------------------------------------------------------------------------------------------------|

| d                           | Number of Demuxes of size D <sub>e</sub> , where e indicates various sizes of Demux in the design |

| α, β, γ                     | Signature variables for physical level watermarking                                               |

| $T_{S}$                     | Tamper tolerance                                                                                  |

| Q                           | Number of distinct variables in the chosen signature for physical level watermarking              |

| Z                           | Size of the signature in physical level watermarking                                              |

| [A] <sub>(I×J)</sub>        | A pixel matrix of image of size I×J                                                               |

| $X_{ij}$                    | A pixel value of the input image where i and j vary from 0 to I-1 and 0 to J-1 respectively       |

| $[F]_{(n \times m)}$        | Kernel matrix of size n×m                                                                         |

| $f_{pq}$                    | Kernel values                                                                                     |

| $O_{\mathrm{w}}$            | Output pixel value                                                                                |

| [O]                         | Output matrix                                                                                     |

| $F^{B}$                     | kernel matrix of a 3×3 blur filter                                                                |

| $F^{S}$                     | kernel matrix of a 3×3 sharpening filter                                                          |

| $F^{VE}$                    | kernel matrix of a 3×3 vertical embossment filter                                                 |

| $F^{HE}$                    | kernel matrix of a 3×3 horizontal embossment filter                                               |

| $F^{ED}$                    | kernel matrix of a 3×3 edge detection filter                                                      |

| $T_{\rm ILB}$               | Total ILBs in a functionally obfuscated design                                                    |

| $T_{DLC}$                   | Total DLCs in a functionally obfuscated DSP core                                                  |

| ω                           | Designer specified tuning variable for DLCs insertion                                             |

| P <sub>v</sub>              | Probability of obtaining valid key in exhaustive trials                                           |

| K <sub>b</sub>              | Total number of key-bits in DLC based logic locking                                               |

| Ens                         | Encryption strength                                                                               |

| $N_{op}^{AES}$              | Number of encrypted output bits generated from AES128                                             |

| N <sup>total</sup><br>kbits | Total number of DLC key bits in a design                                                          |

## **ACRONYMS**

| VLSI         Very Large Scale Integration           IP         Intellectual Property           DSP         Digital Signal Processor           CE         Consumer Electronics           IC         Integrated Circuits           SoC         System on Chip           RTL         Register Transfer Level           VHDL         Very High Speed Integrated Circuit Hardware Description Language           GDS         Graphic Database System           ALU         Arithmetic Logic Unit           DFG         Data Flow Graph           CDFG         Control Data Flow Graph           SDF         Scheduled Data Flow Graph           FSM         Finite State Machine           RE         Reverse Engineering           CS         Control Step           CIG         Colored Interval Graph           UF         Unrolling Factor           3PIP         3rd party Intellectual Property           ASIC         Application Specific Integrated Circuit           PSO         Particle Swarm Optimization           DSE         Design Space Exploration           FU         Functional Unit           HLT         High Level Transformation           opn         Operation | HLS  | High Level Synthesis                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------|

| DSP Digital Signal Processor  CE Consumer Electronics  IC Integrated Circuits  SoC System on Chip  RTL Register Transfer Level  VHDL Very High Speed Integrated Circuit Hardware Description Language  GDS Graphic Database System  ALU Arithmetic Logic Unit  DFG Data Flow Graph  CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3rd party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unvolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                    | VLSI | Very Large Scale Integration                                     |

| CE Consumer Electronics IC Integrated Circuits SoC System on Chip RTL Register Transfer Level VHDL Very High Speed Integrated Circuit Hardware Description Language GDS Graphic Database System ALU Arithmetic Logic Unit DFG Data Flow Graph CDFG Control Data Flow Graph SDFG Scheduled Data Flow Graph FSM Finite State Machine RE Reverse Engineering CS Control Step CIG Colored Interval Graph UF Unrolling Factor 3PIP 3rd party Intellectual Property ASIC Application Specific Integrated Circuit PSO Particle Swarm Optimization DSE Design Space Exploration FU Functional Unit HLT High Level Transformation opn Operation LU Loop Unrolling THT Tree Height Transformation ROE Redundant Operation Elimination LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                           | IP   | Intellectual Property                                            |

| IC Integrated Circuits  SoC System on Chip  RTL Register Transfer Level  VHDL Very High Speed Integrated Circuit Hardware Description Language  GDS Graphic Database System  ALU Arithmetic Logic Unit  DFG Data Flow Graph  CDFG Control Data Flow Graph  SPM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                               | DSP  | Digital Signal Processor                                         |

| SoC System on Chip  RTL Register Transfer Level  VHDL Very High Speed Integrated Circuit Hardware Description Language  GDS Graphic Database System  ALU Arithmetic Logic Unit  DFG Data Flow Graph  CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                       | CE   | Consumer Electronics                                             |

| RTL Register Transfer Level  VHDL Very High Speed Integrated Circuit Hardware Description Language  GDS Graphic Database System  ALU Arithmetic Logic Unit  DFG Data Flow Graph  CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IC   | Integrated Circuits                                              |

| VHDL Very High Speed Integrated Circuit Hardware Description Language GDS Graphic Database System ALU Arithmetic Logic Unit DFG Data Flow Graph CDFG Control Data Flow Graph SDFG Scheduled Data Flow Graph FSM Finite State Machine RE Reverse Engineering CS Control Step CIG Colored Interval Graph UF Unrolling Factor 3PIP 3 <sup>rd</sup> party Intellectual Property ASIC Application Specific Integrated Circuit PSO Particle Swarm Optimization DSE Design Space Exploration FU Functional Unit HLT High Level Transformation opn Operation LU Loop Unrolling THT Tree Height Transformation ROE Redundant Operation Elimination LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SoC  | System on Chip                                                   |

| GDS Graphic Database System  ALU Arithmetic Logic Unit  DFG Data Flow Graph  CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RTL  | Register Transfer Level                                          |

| ALU Arithmetic Logic Unit  DFG Data Flow Graph  CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VHDL | Very High Speed Integrated Circuit Hardware Description Language |

| DFG Data Flow Graph  CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3rd party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GDS  | Graphic Database System                                          |

| CDFG Control Data Flow Graph  SDFG Scheduled Data Flow Graph  FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3rd party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ALU  | Arithmetic Logic Unit                                            |

| SDFG Scheduled Data Flow Graph FSM Finite State Machine RE Reverse Engineering CS Control Step CIG Colored Interval Graph UF Unrolling Factor 3PIP 3rd party Intellectual Property ASIC Application Specific Integrated Circuit PSO Particle Swarm Optimization DSE Design Space Exploration FU Functional Unit HLT High Level Transformation opn Operation LU Loop Unrolling THT Tree Height Transformation ROE Redundant Operation Elimination LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DFG  | Data Flow Graph                                                  |

| FSM Finite State Machine  RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CDFG | Control Data Flow Graph                                          |

| RE Reverse Engineering  CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SDFG | Scheduled Data Flow Graph                                        |

| CS Control Step  CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FSM  | Finite State Machine                                             |

| CIG Colored Interval Graph  UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RE   | Reverse Engineering                                              |

| UF Unrolling Factor  3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CS   | Control Step                                                     |

| 3PIP 3 <sup>rd</sup> party Intellectual Property  ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CIG  | Colored Interval Graph                                           |

| ASIC Application Specific Integrated Circuit  PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UF   | Unrolling Factor                                                 |

| PSO Particle Swarm Optimization  DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3PIP | 3 <sup>rd</sup> party Intellectual Property                      |

| DSE Design Space Exploration  FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ASIC | Application Specific Integrated Circuit                          |

| FU Functional Unit  HLT High Level Transformation  opn Operation  LU Loop Unrolling  THT Tree Height Transformation  ROE Redundant Operation Elimination  LICM Loop Invariant Code Motion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PSO  | Particle Swarm Optimization                                      |