# ENCODED ENCRYPTION AND BIOMETRICS FOR HIGH-LEVEL SYNTHESIS BASED HARDWARE SECURITY AGAINST IP PIRACY AND FRAUD IP OWNERSHIP

### **A THESIS**

Submitted in fulfilment of the requirements for the award of the degree of

**Master of Science (Research)**

by

**Bharath Kollanur**

# DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE

<MONTH AND YEAR OF THESIS SUBMISSION>

## INDIAN INSTITUTE OF TECHNOLOGY INDORE

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled ENCODED ENCRYPTION AND BIOMETRICS FOR HIGH-LEVEL SYNTHESIS BASED HARDWARE SECURITY AGAINST IP PIRACY AND FRAUD IP OWNERSHIP in the fulfilment of the requirements for the award of the degree of MASTER OF SCIENCE (RESEARCH) and submitted in the DISCIPLINE OF COMPUTER SCIENCE AND ENGINEERING, Indian Institute of Technology Indore, is an authentic record of my own work carried out during the time period from August 2021 to < Month and year of MS (Research) Thesis submission> under the supervision of Dr Anirban Sengupta, Associate Professor, and <Affiliation>

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

Signature of the student with date

BHARATH KOLLANUR

This is to certify that the above statement made by the candidate is correct to the best of my/our knowledge.

Signature of the Supervisor of MS (Research) thesis (with date)

DR ANIRBAN SENGUPTA

.\_\_\_\_\_

# **BHARATH KOLLANUR** has successfully given his/her MS (Research) Oral Examination held on **<Date of MS (Research) Oral Examination>**.

| Signature of Chairperson (OEB) with date | Signature(s) of Thesis Supervisor(s) with date |

|------------------------------------------|------------------------------------------------|

| Signature of Convener, DPGC with date    | Signature(s) of head of Discipline with date   |

### **ACKNOWLEDGEMENTS**

Completing a thesis is a challenging and demanding journey that requires perseverance, hard work, and support from many individuals. As I look back at my journey, I am grateful to the many people who have played a significant role in making this accomplishment possible.

Firstly, I would like to express my deepest gratitude to my thesis advisor, Prof Anirban Sengupta, for their guidance, patience, and support throughout my research journey. Their insightful feedback, constructive criticism, and expertise have been invaluable in shaping the direction and scope of my work. I am grateful for the opportunities and challenges they provided me and their unwavering encouragement and support during good and difficult times.

I would like to thank my lab seniors Mr Rahul Chaurasia and Mr Aditya Anshul for their invaluable guidance, mentoring, and support during my research journey. Their expertise, and dedication to their work have been a constant source of inspiration for me, and I have learned so much from their vast knowledge and experience. Their continuous encouragement and motivation have been instrumental in shaping my research work and career goals. I would also like to extend my gratitude to my lab senior Dr Mahendra Rathor, who has passed out from our lab. Their invaluable contributions, advice, and support have played a signification role in shaping my research journey. Their experiences, insights, and guidance have been a valuable asset, and I am grateful for their continuous support and encouragement.

I would also like to thank the members of my thesis committee, Prof Abhishek Srivastava, Prof Somaditya Sen, Prof Somnath Dey, Prof Neminath Hubballi, and Prof Aniruddha Singh Kushwaha, for their valuable feedback, critical evaluation, and insightful suggestions. Their expertise and guidance helped me navigate through the complexities of the research process and provided me with the necessary guidance to produce a quality thesis. I would like to express my heartfelt thanks to the faculty and staff of the Computer Science and Engineering department at IIT Indore for providing me with a stimulating and supportive environment to pursue my research work. I am grateful for the resources, infrastructure and opportunities provided to me by the department which have been instrumental in shaping my research journey.

I am also deeply grateful to my family and friends for their love, encouragement, and unwavering support throughout my academic journey. Their patience, understanding, and motivation have been the driving force behind my success. I particularly acknowledge my parents, Raja Kumar and Manjula, and my brother, Dr Charan, for their endless support, encouragement, and belief in me. I am also grateful to Vaishnavi and Shibani Das, for their love, encouragement, and unwavering support.

Lastly, I would like to express my gratitude to all the individuals who have helped me in various ways during my research journey, including my peers, colleagues, and other professionals who have provided me with their valuable insights, support, and assistance.

Completing this thesis has been a challenging but rewarding experience, and I am grateful to everyone who has contributed to my journey.

### **ABSTRACT**

This thesis presents two novel methodologies for securing intellectual property (IP) core designs against hardware security threats. The first methodology is a quadruple-phase watermarking technique for securing hardware IP cores during high-level synthesis (HLS), while the second methodology explores unified biometrics with an encoded dictionary for the hardware security of fault-secured digital signal processing (DSP) intellectual property (IP) core designs.

The first methodology addresses the issue of IP piracy and ownership infringement that poses a significant threat to the security of authentic IP vendors. The proposed quadruple-phase watermarking technique employs graph portioning, encoding tree, and eightfold mapping to generate a robust watermarking signature. The signature is embedded at four stages of HLS, including scheduling, register binding, resource binding, and interconnect binding, to ensure high-quality hardware security constraints. The results demonstrate a considerable decrease in the probability of coincidence and a higher level of tamper tolerance compared to the state-of-the-art techniques, without incurring a significant design cost overhead.

The second methodology focuses on the hardware security of fault-secured digital signal processing (DSP) intellectual property (IP) core designs against IP piracy. The methodology exploits scheduled and allocated DSP design using a behavioural synthesis process to generate a fault-secured DSP IP core. The proposed technique embeds encoded unified biometric-based hardware security constraints into the design to provide a detective control mechanism against IP piracy. This results in the generation of protected fault-secured DSP designs against IP piracy, ensuring the safety of end consumers against pirated and unreliable designs

by isolating them before integration into the system-on-chips of consumer electronics (CE) systems.

Overall, both methodologies address the critical issue of IP piracy and ownership infringement that sabotage the revenue and reputation of genuine IP vendors. The proposed techniques provide a higher level of security with a low probability of coincidence and high tamper tolerance, without incurring significant design cost overhead. These methodologies pave the way for more robust and secure IP designs, thereby ensuring the safety and security of end consumers.

### LIST OF PUBLICATIONS

- Mahendra Rathor, Aditya Anshul, K Bharath, Rahul Chaurasia, Anirban Sengupta, "Quadruple Phase Watermarking during High-Level Synthesis for Securing Reusable Hardware IP Cores", Elsevier Journal on Computers and Electrical Engineering, Volume 105, January 2023, 108476

- Aditya Anshul, K Bharath, Anirban Sengupta, "Designing a Low Cost Secured DSP Core Using PSO-DSE Driven Steganography for CE Systems", *Proceedings of 8th IEEE International Symposium on Smart Electronic Systems (IEEE iSES)*, India, Dec 2022, pp. 95-100, doi: 10.1109/iSES54909.2022.00030

### **TABLE OF CONTENTS**

| LIS | ST OF FIGURESxi                                                    |

|-----|--------------------------------------------------------------------|

| LIS | ST OF TABLES xiii                                                  |

| NO  | MENCLATURE xv                                                      |

| AC  | RONYMS xvi                                                         |

|     |                                                                    |

|     | apter 1: Introduction 1                                            |

| 1.1 | Overview                                                           |

| 1.2 | Evolution of IP Core Design                                        |

| 1.3 | The Advantages of Third-Party IP Core Suppliers                    |

| 1.4 | Security Concerns and Piracy Issues of Reusable IP Cores in the    |

|     | Global SoC Supply Chain6                                           |

| 1.5 | Safeguarding Intellectual Property: An Examination of Available IP |

|     | Protection Methods                                                 |

| 1.6 | Background on High-Level Synthesis                                 |

| 1.7 | Organisation of the Thesis                                         |

| Cha | apter 2: Review of Past Work and Problem Formulation 17            |

| Cha | apter 3: Quadruple phase watermarking during high level synthesis  |

|     | for securing reusable hardware intellectual property cores 24      |

| 3.1 | Overview of the proposed approach                                  |

| 3.2 | Partitioning of Scheduled Data Flow Graph (SDGF)                   |

| 3.3 | The proposed signature generation process                          |

| Cha | apter 4: Signature embedding and detection process in the          |

|     | quadruple phase watermarking approach during high level            |

|     | synthesis 37                                                       |

| 4 1 | The proposed signature embedding process                           |

| 4.2 Embedding constraints in the scheduling phase (phase-1) 39              |

|-----------------------------------------------------------------------------|

| 4.3 Signature detection in the proposed watermarking approach 48            |

|                                                                             |

| <b>Chapter 5: Exploring Unified Biometrics with Encoded Dictionary</b>      |

| for Hardware Security of Fault Secured IP Core Designs 52                   |

| 5.1 Proposed hardware security methodology for securing fault-secured       |

| DSP IP core                                                                 |

| 5.2 Generating transient fault secured DSP designs                          |

| 5.3 Multimodal biometric signature generation                               |

|                                                                             |

| Chapter 6: Unified biometric signature generation using expandable          |

| encoded dictionary and signature embedding and detection                    |

| process 70                                                                  |

| 6.1 Proposed Expandable Encoded Dictionary                                  |

| 6.2 Embedding unified biometric signature of IP vendor into the             |

| design                                                                      |

| 6.3 Detection of pirated design using the proposed methodology 77           |

| 6.4 Security properties of encoded dictionary-based unified biometrics . 78 |

|                                                                             |

| Chapter 7: Results and Discussion/Analysis 81                               |

| 7.1 Results and analysis of the proposed quadruple phase watermarking       |

| approach                                                                    |

| 7.2 Results and analysis of the proposed unified biometric driven hardware  |

| security methodology89                                                      |

|                                                                             |

| Chapter 8: Conclusions and Scope for Future Work 95                         |

|                                                                             |

| REFERENCES 98                                                               |

### **LIST OF FIGURES**

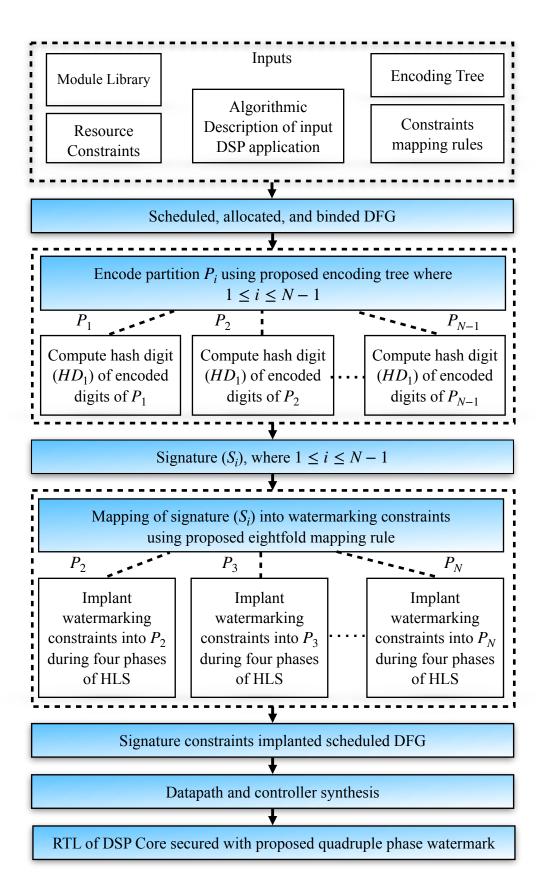

| 3.1  | Flow diagram of proposed quadruple phase watermarking                    |

|------|--------------------------------------------------------------------------|

|      | approach                                                                 |

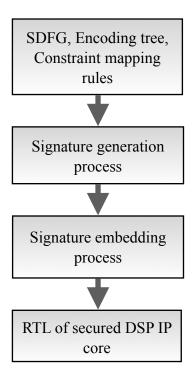

| 3.2  | Abstract view of the proposed quadruple phase watermarking               |

|      | approach                                                                 |

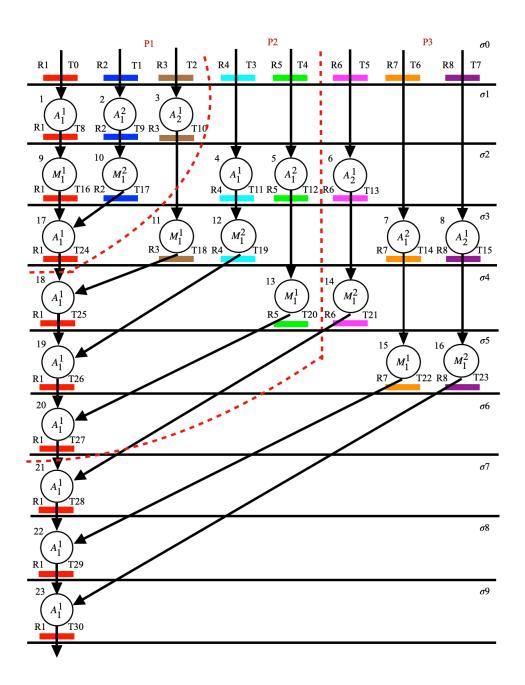

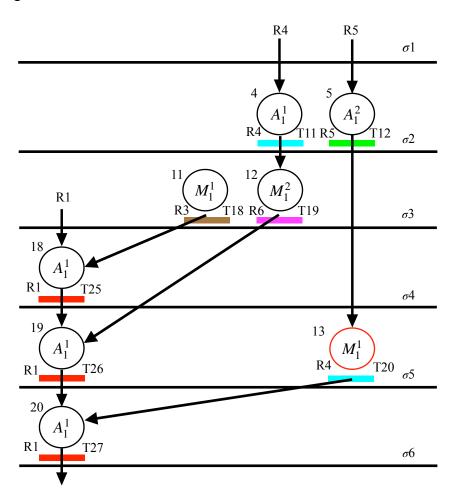

| 3.3  | Scheduled Data Flow Graph (SDFG) of FIR core with partitions P1,         |

|      | P2, and P3                                                               |

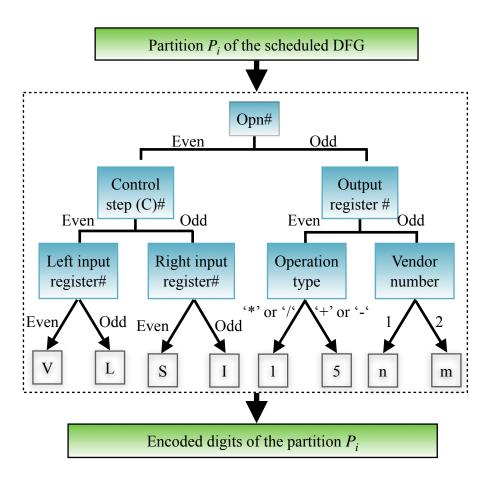

| 3.4  | Proposed encoding tree used or encoding partitions of SDFG 33            |

| 3.5  | Traversal details of operations in the partition $P_1$ of SDFG along the |

|      | proposed encoding tree                                                   |

| 4.1  | Post-embedding scheduling constraints in the partition $P_2$ of the      |

|      | SDFG                                                                     |

| 4.2  | CIG of partition $P_2$ of SDFG post-embedding scheduling                 |

|      | constraints                                                              |

| 4.3  | CIG of partition $P_2$ of SDFG post-embedding register binding           |

|      | constraints                                                              |

| 4.4  | Post-embedding register binding constraints in partition $P_2 \dots 43$  |

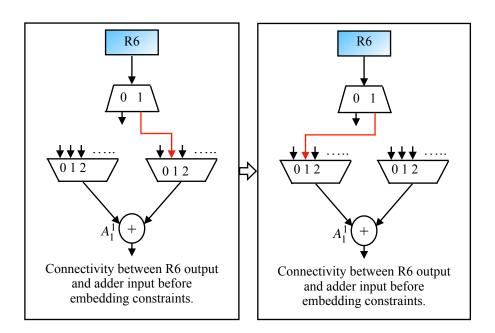

| 4.5  | Embedding of constraints in interconnect binding phase, on RTL 44        |

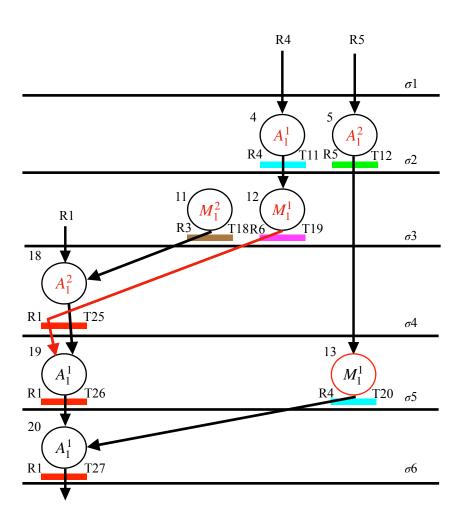

| 4.6  | SDFG of partition $P_2$ post-embedding signature $S_1$ generated from    |

|      | partition $P_1$                                                          |

| 4.7  | Signature generation and embedding flow of proposed quadruple            |

|      | phase watermarking approach                                              |

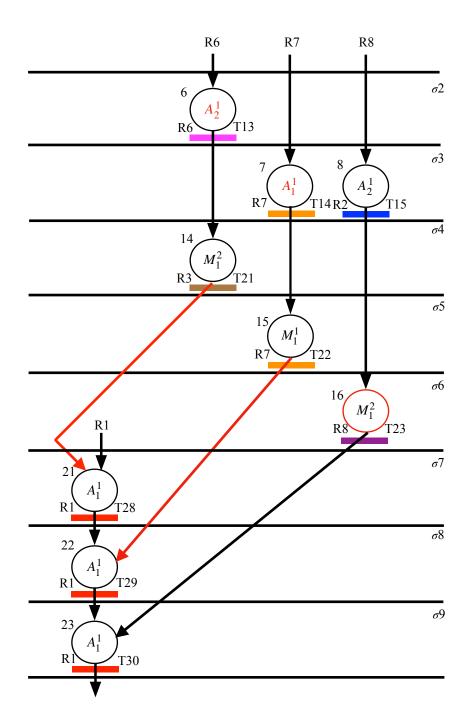

| 4.8  | SDFG of partition $P_3$ post-embedding signature $S_2$ generated from    |

|      | partition $P_2$                                                          |

| 4.9  | SDFG of FIR core after embedding a watermark                             |

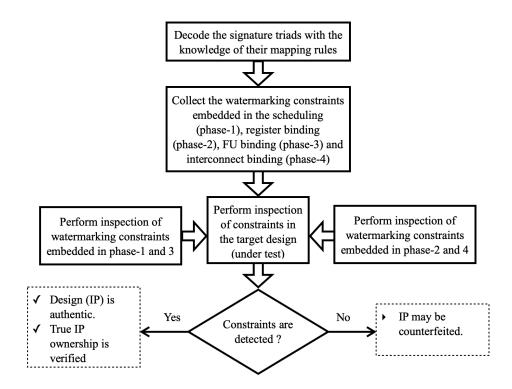

| 4.10 | Signature detection using the proposed approach for authentic IP         |

|      | verification                                                             |

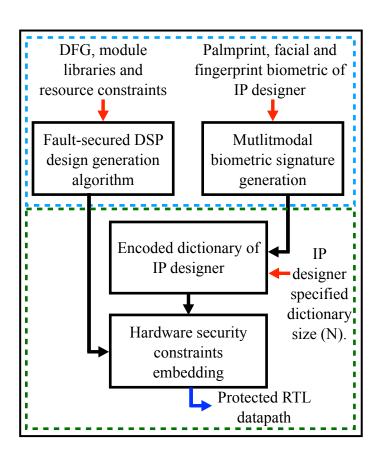

| 5 1  | Overview of the proposed methodology                                     |

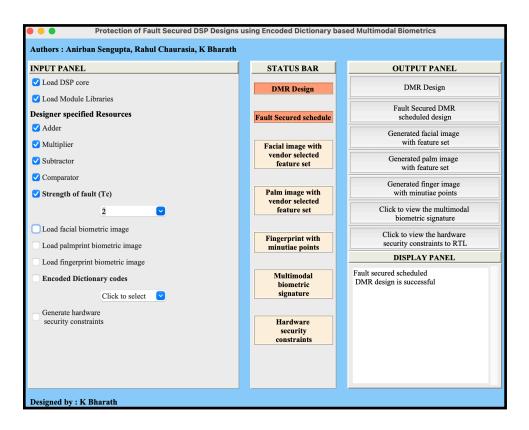

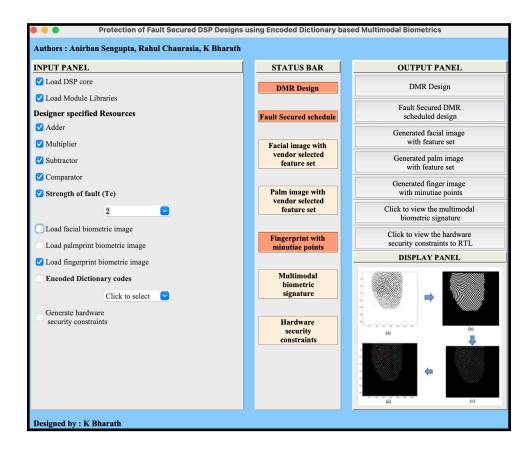

| 5.2   | Screenshot of the hardware security tool demonstrating the successful |

|-------|-----------------------------------------------------------------------|

|       | generation of fault-secured DMR design of 8-point IDCT DSP            |

|       | core                                                                  |

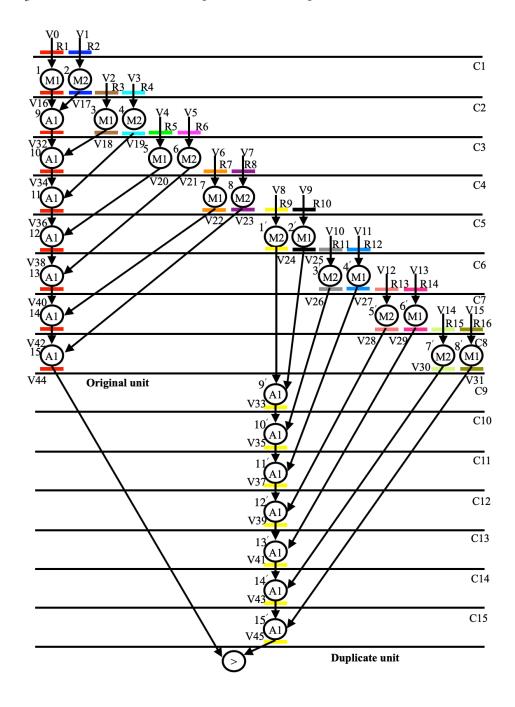

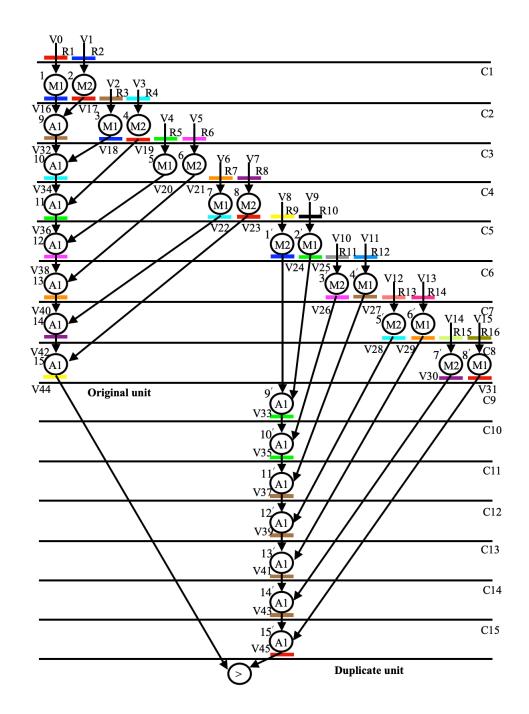

| 5.3   | Fault-secured scheduled IDCT filter design (pre-embedding security    |

|       | constraints)                                                          |

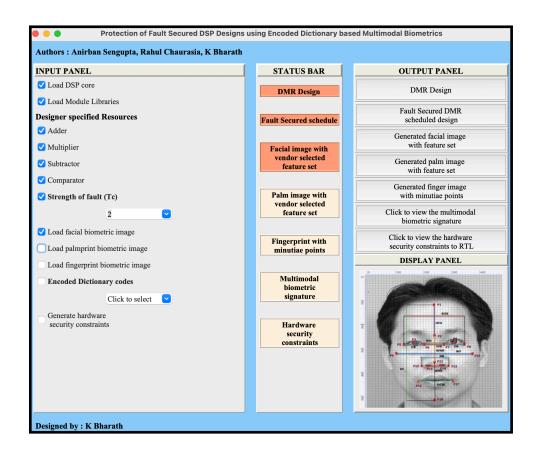

| 5.4   | Screenshot of hardware security tool corresponding to the facial      |

|       | image with the vendor-selected feature set on the display panel 64    |

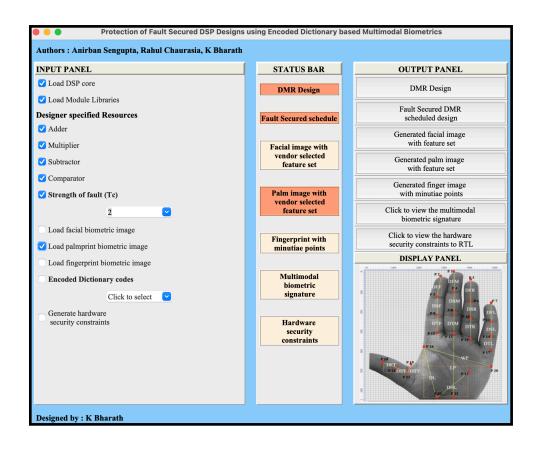

| 5.5   | Screenshot of hardware security tool corresponding to the palmprint   |

|       | image with the vendor-selected feature set on the display panel 66    |

| 5.6   | Screenshot of hardware security tool corresponding to the fingerprint |

|       | image with minutiae points on the display panel                       |

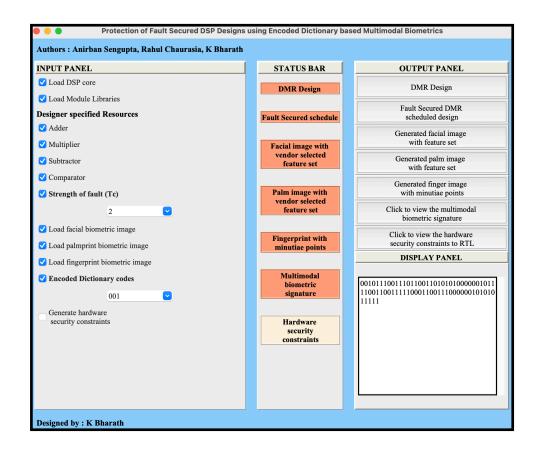

| 6.1   | Screenshot of hardware security tool corresponding to the encoded     |

|       | unified biometric signature                                           |

| 6.2   | Fault-secured scheduled IDCT filter design (post-embedding security   |

|       | constraints)                                                          |

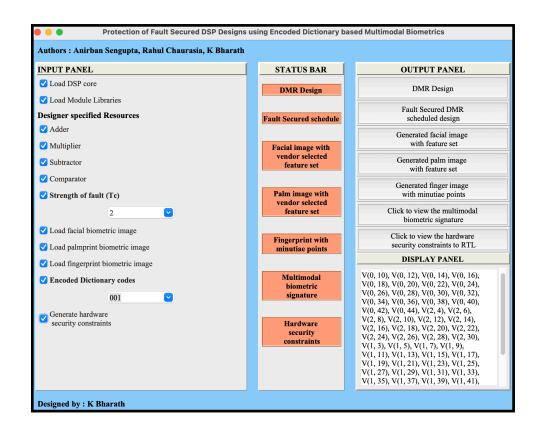

| 6.3   | Screenshot of hardware security tool corresponding to the hardware    |

|       | security constraints                                                  |

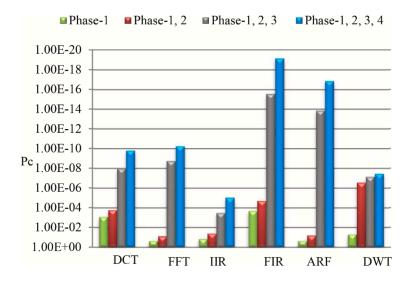

| 7.1.  | 1 Variation in Pc due to embedding watermark during different         |

|       | phases                                                                |

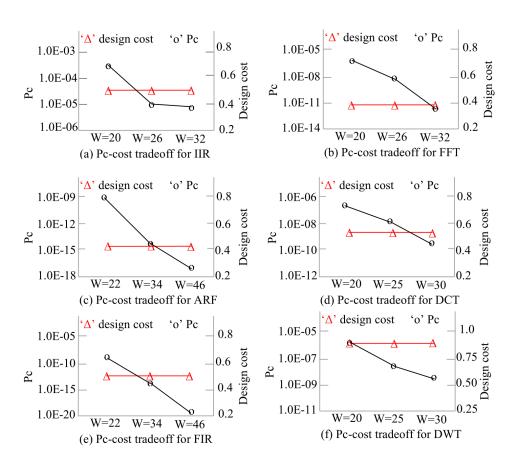

| 7.1.2 | 2 Security (in terms of Pc)-cost tradeoff for various benchmarks 87   |

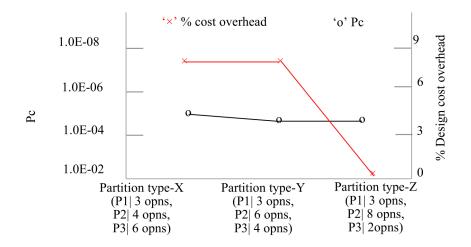

| 7.1.  | 3 Partitioning-cost trade-off for IIR filter core for signature       |

|       | size=32                                                               |

### **LIST OF TABLES**

| 4.1   | Mapping triads in the signature into the hardware security              |

|-------|-------------------------------------------------------------------------|

|       | constraints                                                             |

| 4.2   | Watermarking constraints for embedding in the partition $P_3 \dots 48$  |

| 5.1   | Signature generation corresponding to the facial features 63            |

| 5.2   | Signature generation corresponding to the palmprint features 65         |

| 5.3   | Signature generation corresponding to fingerprint minutiae points . 68  |

| 6.1   | Encoded dictionary for 3-bits (N=3) (expandable up to $2^N$ encoding    |

|       | rules)                                                                  |

| 6.2   | Register allocation table for pre-embedding unified biometric           |

|       | signature into the design                                               |

| 6.3   | Register allocation table for pre-embedding unified biometric           |

|       | signature into the design                                               |

| 7.1.  | Probability of coincidence (Pc) analysis of proposed approach w.r.t.    |

|       | related approaches [11,12,15]                                           |

| 7.1.2 | 2 Comparison of $P_C$ of the proposed approach with [40, 17] 84         |

| 7.1.3 | 3 Tamper tolerance $(T^P)$ analysis of proposed approach w.r.t. related |

|       | approaches [11], [12], [15]                                             |

| 7.1.4 | 4 Design cost pre and post-embedding of the proposed watermark 88       |

| 7.2.  | 1 Comparison of $Pb_c$ of proposed unified biometrics approach w.r.t    |

|       | related works [11], [17]                                                |

| 7.2.2 | 2 Comparison of $Pb_c$ of proposed unified biometrics approach w.r.t    |

| relat | ted works [26], [28]                                                    |

| 7.2.3 | 3 Comparison of $TT$ of proposed unified biometrics approach w.r.t      |

|       | related works [11], [17]                                                |

| 7.2.4 | 4 Comparison of $TT$ of proposed unified biometrics approach w.r.t      |

|       | related works [26], [28]                                                |

| 7.2.5 $Pb_c$ , TT of the proposed approach corresponding to varying signature |

|-------------------------------------------------------------------------------|

| size for 8-point DCT application                                              |

| 7.2.6 Comparison of the design cost pre and post-embedding encoded            |

| dictionary-based unified biometric signature                                  |

| 7.2.7 Implementation run time of the proposed security methodology            |

| corresponding to different benchmarks (fault-secured)                         |

### **Nomenclature**

$P_i$  — Partition of the Scheduled Data Flow Graph (SDFG)

$S_i$  — Signature generated from the partition  $P_i$

$HD_i$  — Hash digest.

$V_i$  — Vendor

$\sigma_i$  — Control step in the SDFG

Ti — Storage variables

Ri — Registers

$A_i^j$  — Adder of jth vendor

$M_i^j$  — multiplier of *j*th vendor

$T_c$  — Transient fault strength

$R_c$  — Resource constraints

$XR_a$  — 'X' represents the number of hardware units and 'a' represents the type of hardware resource.

$N_{OG}$  — Original unit

$N_{DP}$  — Duplicate unit

Ci — Control step in SDFG

Vi — Storage variables

CN — Crossing number

*P<sub>c</sub>* — Probability of coincidence

$T^p$  — Tamper tolerance

$C_t$  — Design cost

$A_H$  — Design area

$L_h$  — Design latency

$Pb_c$  — Probability of coincidence of the fault secured DSP

TT — Tamper tolerance of the fault-secured DSP design

$D_c(s_n^t)$  — Design cost of the fault-secured DSP design

### **ACRONYMS**

DSPs — Digital Signal Processors

DSP — Digital Signal Processing

VHDL — Very High-Speed Integrated Circuit Hardware Description

Language

FPGAs — Field Programmable Gate Arrays

ASICs — Application-Specific-Integrated-Circuits

CPU — Central Processing Unit

IP — Intellectual Property

HLS — High-Level Synthesis

IoT — Internet of Things

SoC — System-on-Chip

IP-XACT — Intellectual Property Core Provider's Group

SIP — Silicon Intellectual Property

CE — Consumer Electronics

CFE — Computational Forensic Engineering

HDL — Hardware Description Language

RTL — Register-Transfer Level

DFG — Data Flow Graph

CFG — Control Flow Graph

CDFG — Control/Data Flow Graph

DSE — Design Space Exploration

PUFs — Physically Unclonable Functions

CED — Concurrent Error Detection

DMR — Dual Modular Redundancy

EM — Electromagnetic

FU — Functional Unit

IC — Integrated Circuit

SDFG — Scheduled Data Flow Graph

FIR — Finite Impulse Response

ET — Encoding Tree

Opn — Operation

CIG — Coloured Interval Graph

SEU — Single-Event Upsets

IDCT — Inverse Discrete Cosine Transform

FFT — Fast Fourier Transform

CN — Crossing Number

DCT — Discrete Cosine Transform

JPEG — Joint Photographic Experts Group

IIR — Infinite Impulse Response

MPEG — Moving Picture Experts Group

### Chapter 1

### Introduction

### 1.1 Overview

Digital Signal Processors (DSPs) are specialised processors designed to perform mathematical operations on real-time signals quickly and efficiently, typically used in various real-time applications. DSPs enhance sound and speech quality in audio and speech processing, while in telecommunications, they process signals for communication systems, in RADAR, LIDAR, and sensors, DSPs are used to process signals for various applications such as navigation, mapping, and object detection. In image and visual processing, they are used to enhance the image and video quality, while in neural network processing, they are used to perform realtime inferencing of deep learning models. DSPs can be found in a variety of devices, ranging from consumer electronics such as mobile phones to satellites and military communications. The widespread use of DSP technology highlights its importance in enabling advanced capabilities in consumer electronics. The first DSP was created by Texas Instruments and was famously used in the child's toy "The Speak & Spell" in the late 1970s. The DSP in the toy was used for speech processing, which allowed the toy to recognise and produce speech sounds. This marked the beginning of the widespread use of DSPs in consumer electronics, and since then, DSPs have become an essential component in many different fields and applications.

Digital Signal Processing (DSP) algorithms are crucial for a variety of applications such as image and audio processing, compression and denoising as mentioned earlier. These algorithms require high performance and low power consumption, which can be achieved through hardware acceleration. One way to achieve hardware acceleration is by using reusable intellectual property (IP) cores. An IP core, or Intellectual property core, is a pre-designed and pre-verified block of digital logic that can be easily integrated into a larger system to perform specific functions. IP cores are designed to be reused in multiple applications, allowing designers to save time and resources while achieving high performance and low power consumption. Reusable IP cores are typically designed in a standard digital design language, such as Very High-Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog, and can be implemented on Field Programmable Gate Arrays (FPGAs) or Application-Specific-Integrated-Circuits (ASICs).

The CPU (Central Processing Unit) and a reusable DSP IP Core are both components used in digital signal processing (DSP) applications, but they have some key differences. A CPU is a computer's main processor that executes instructions and performs data processing. It is designed to perform a wide range of tasks and can be programmed to perform DSP algorithms, but it is not optimised for DSP processing. The CPU is a general-purpose processor that can handle a wide range of tasks, but its processing speed and power consumption for DSP algorithms can be relatively slow compared to dedicated DSP hardware. On the other hand, a reusable DSP IP Core is a predesigned and pre-verified block of digital logic that is optimised specifically for DSP processing. It can be integrated into larger systems and provides faster processing speeds and lower power consumption compared to CPU-based implementation of the same DSP algorithm. A reusable DSP IP Core is designed to perform a specific DSP function and can be optimised for high performance and low power consumption, making it a better choice for DSP applications than a general-purpose CPU.

Reusable IP cores offer several advantages over traditional software-based implementations of DSP algorithms. In hardware, they can be implemented in parallel, which eliminates the overhead of software-based processing. IP cores are optimised for low power consumption, which is important for battery-powered devices or applications that need to minimise power consumption. Another advantage of reusable IP Cores is their ease of integration into larger systems. IP Cores can be used as building blocks for larger systems, reducing design time and increasing design reliability. This allows designers to focus on the overall system design rather than on implementing individual DSP algorithms. With the growing demand for high-performance and low-power computing systems, reusable IP cores will likely become increasingly widespread in the future.

### 1.2 Evolution of IP Core Design

The evolution of IP (Intellectual Property) core design has been driven by the increasing complexity of integrated circuits and the need for more efficient and cost-effective design methods. IP Core design is a methodology for creating reusable blocks of digital logic that can be used in the design of integrated circuits. Over the past several decades, IP Core design has evolved to meet the changing needs of chip designers and the wider electronics industry. The early days of IP Core design were characterised by the use of hardware description languages such as VHDL and Verilog. Designers would use these languages to create digital logic circuits from scratch, using a combination of manual design and simulation tools. While this approach was effective for relatively simple circuits, it became increasingly time-consuming and complex as integrated circuits became more complex. In response to these challenges, IP Core design began to evolve towards a more automated and efficient approach. The introduction of High-Level Synthesis (HLS) tools allowed designers to describe the functionality of a digital logic circuit using a high-level programming language, such as C or C++, rather than hardware description languages. This reduced the time and effort required to create digital logic and improved the final product's quality and reliability, as HLS tools used advanced algorithms to generate optimised digital logic.

The increasing importance of low-power and energy-efficient design has also played a key role in the evolution of IP Core design. Many IP Cores are now designed specifically to minimise power consumption, and their use in a design can help reduce the system's overall power consumption. This is especially important for battery-powered mobile devices, where power consumption is a critical consideration. The rise of the Internet of Things (IoT) and the increasing demand for connected devices have led to a growth in the use of IP Cores for embedded systems. IP cores are being used to address the need for high performance, low area, minimum cost, and timely operation in many embedded systems, especially in mobile phones, where low power consumption and high performance are critical requirements. Another key development in IP Core design was the introduction of platform-based design. Platform-based design enables designers to reuse common components and systems across multiple applications, reducing development time and cost and improving the quality and reliability of the final product. This approach also allows for easier integration of IP Cores from different sources, making it easier for designers to access a wide range of high-quality, reusable IP Cores.

Further, the growing demand for IP Cores led to the development of IP Core libraries that could be easily integrated into a larger System-on-Chip (SoC) design. These libraries allowed designers to quickly and easily access a range of IP Cores, speeding up the design process and reducing the time to market for a product. The development of IP Core libraries was a significant milestone in the evolution of IP Core design, as it allowed designers to take advantage of pre-existing IP Cores and focus on the

overall system design. The evolution of IP Core design has also led to the development of IP Core standards, such as the Intellectual Property Core Provider's Group (IP-XACT) standards. IP-XACT provides a standardised format for describing IP Cores, making it easier for designers to integrate IP Cores from different vendors into a larger SoC design. The standardisation of IP cores has also enabled the creation of IP Core exchange platforms, such as the Silicon Intellectual Property (SIP) Core Exchange, where designers can easily access and compare IP Core from different vendors.

## 1.3 The Advantages of Third-Party IP Core Suppliers

IP Cores are supplied by third-party IP vendors for several reasons:

- Specialist expertise: IP vendors specialise in designing and developing specific IP Cores, allowing them to focus on the latest technological advancements and provide their customers with high-quality, reliable IP Cores.

- 2. Cost-effectiveness: Designing IP cores from scratch is a time-consuming and resource-intensive process. By outsourcing this work to third-party IP vendors, companies can take advantage of the lower costs associated with specialised design teams and reduce the time and effort required to bring a product to market.

- Time-to-market: IP vendors have a pre-existing library of IP Cores, which can be used to speed up the development process and reduce the time to market for a product.

- 4. Risk reduction: IP Cores are thoroughly tested and validated before they are made available to customers, reducing the risk of design bugs and improving the quality and reliability of the final product.

- 5. Scalability: IP vendors have the resources and expertise to scale up the production of IP cores as demand increases, enabling customers to take advantage of economies of scale and reduce costs.

In summary, IP Cores are supplied by third-party IP vendors because they offer a cost-effective solution that reduces design time and risk, and improves quality while allowing companies to focus on the overall system design. By outsourcing IP Core development to specialist vendors, companies can take advantage of the latest technology advancements and bring their products to market more quickly.

# 1.4 Security Concerns and Piracy Issues of Reusable IP Cores in the Global SoC Supply Chain

The integration of Intellectual Property (IP) Cores in System-on-Chip (SoC) [1] design has become a standard practice in the consumer electronics (CE) industry. The use of IP Cores, supplied by third-party IP vendors [2], maximises design productivity and minimises design time. These hardware IP cores are designed to perform specific functions and are often reused in various electronic designs. The increasing reuse of IP Cores has brought to the forefront of the security concerns and IP piracy issues that arise from the global SoC supply chain. The reuse of IP Cores is driven by several benefits, including reduced development time and cost, improved design quality, and reduced risk. However, this increased reuse of IP cores leads to risks like copying and piracy. IP Cores can represent many man-years of design, research, and verification testing; therefore, it is essential to protect this investment. If IP Cores are not properly secured, they can easily be copied and used without authorisation, resulting in significant financial losses for the original IP Core developer.

One of the primary security concerns in the global SoC supply chain is the potential for IP Core tampering. Tampering with IP Cores can take many forms, including unauthorised modifications, insertion of malicious code, or unauthorised copying. This can lead to significant security breaches, particularly if the IP Cores are used in critical systems such as those found in the aerospace, defence, or medical industries. Another security concern in the global SoC supply chain is the potential for IP Core counterfeiting. Counterfeit IP Cores can be difficult to detect and can have serious consequences for the end user. Counterfeit IP Cores may not perform as intended, contain malicious code, or may not comply with industry standards. This can lead to significant safety and security risks and financial losses for the end user [2, 3, 4, 5].

Another major concern is the infringement of the licensing agreement through the utilisation of the IP Core in multiple products with only a single license obtained. This is a common occurrence, as IP Core providers often sub-license other IP Cores for inclusion in their designs, and once ad design has completed testing and verification, it is tempting to reuse it in additional products. This poses a significant threat to the original IP owner, as their investment in the design and development of the core is not protected. In addition to the threat of license violations, there is also the risk of direct piracy, where fraudulent means or reverse engineering may allow the direct theft or copying of the IP for reuse without permission. In such cases, the adversary may even claim the IP to be their own, making it difficult for the original IP owner to prove ownership and protect their investment. Unauthorised duplication and distribution of IP Cores can lead to significant financial losses for the owners and undermine their competitive advantage in the market.

Intellectual Property (IP) Cores are critical components in the design of silicon chips and play a crucial role in the electronics industry. These cores contain valuable technology, trade secrets, and propriety information that are the result of extensive research and development efforts. Protecting IP Cores from securing concerns and piracy issues is

vital to ensure companies' financial stability and competitiveness in the chip industry.

### 1.5 Safeguarding Intellectual Property: An Examination of Available IP Protection Methods

The use of IP protection mechanisms is critical in ensuring the protection of IP Cores from security concerns and piracy issues. The different protection mechanisms provide different levels of protection based on the design abstraction levels. A comprehensive IP protection strategy can be achieved by combining these mechanisms. Understanding the different protection mechanisms and their benefits is crucial for companies in the chip design industry, as it can help them to better protect their valuable IP assets. Some well-known IP Protection mechanisms widely used in various consumer electronics (CE) products include watermarking, IP metering, Computational Forensic Engineering (CFE), and patents and copyrights.

### Watermarking

The insertion of additional watermarking constraints is a widely used method for protecting Intellectual Property (IP) Cores in recent years. This method is implemented during the architectural synthesis stage of IP design, specifically in the register allocation or scheduling step. In this process, a coloured interval graph is used to represent the storage variables and their overlapping lifetimes. By adding additional edges between the nodes of the graph as watermarking constraints, the storage variable is forced to be stored in distinct registers, thus increasing the security of the signature. The watermarking scheme requires a signature detection process which is done in two steps: reverse engineering and signature verification. Reverse engineering involves obtaining a sample of the product suspected of using the IP illegally and sending it to a specialist laboratory for analysis and reverse engineering. Signature verification involves comparing the

detected signature with the original signature to confirm the presence of the IP in the product. This method of IP protection offers a secure and reliable way to protect the IP from security concerns and piracy issues, ensuring that the owner's rights are protected.

### **IP Metering**

IP metering is a technique used by IP vendors to control and monitor the usage of their intellectual property (IP) Cores. IP metering aims to ensure that IP vendors receive fair compensation for their work and to prevent the unauthorised or illegal use of their IP. IP metering is performed by assigning a unique identifier to each unit of the IP Core. This identifier can be created through a variety of methods, including different configurations during architectural synthesis or programmable hardware elements. The unique identifier acts as a meter that records the usage of the IP and enables the IP vendor to enforce royalties for each unit sold. Hardware and software metering are techniques used to protect IP cores from piracy and illegal use. Hardware metering is employed in situations where the design company does not have control over the number of copies being made by the silicon foundry. In the case of software IP Core vendors, the number of uses of the soft core can be metered to ensure that the user is not making unauthorised copies. This is achieved through the use of hardware/software locks and license agreements. Hardware metering is performed by making a small portion of the design programmable during configuration time. This small portion is configured in a unique way for each manufactured chip, allowing the manufacturer to determine the number of units (or batches of units) produced. On the other hand, software metering involves tracking the number of uses of the software IP Core by the user through the use of license agreements.

IP metering is an important tool for IP protection, as it helps to ensure that IP vendors are properly compensated for their work. This not only protects their investment in the development of the IP Core but also incentivises further innovation and investment in the field. In addition to enforcing royalties, IP metering also provides IP vendors with a level of control and monitoring over the usage of their IP. This helps to prevent piracy and unauthorised use, ensuring that IP vendors' rights are protected and safeguarding their investment in the development of the IP Core.

### **Computational Forensic Engineering (CFE)**

Computational Forensic Engineering (CFE) involves the collection of features and statistics of a given IP design, which can be analysed to determine the likelihood of a specific entity having created it. In the next phase, the collected features and statistics are extracted to determine the unique characteristics of the design. The extracted features are then clustered and compared to a pool of algorithms used to solve the same optimisation problem, to identify the algorithm that has been used to create the IP design. Finally, the results are validated to ensure the accuracy and reliability of the findings. The use of CFE helps in identifying the entity responsible for creating a particular IP design, thereby providing a way to enforce IP rights and prevent piracy issues.

### **Patent and Copyright**

A patent serves as a form of intellectual property protection that gives the inventor the exclusive right to prevent others from making, using, selling, and importing the patented invention for a specified number of years. This helps the inventor to protect their innovations and prevent others from profiting from their work without their permission. Obtaining a pater requires a thorough examination process, including a search for prior art, to determine the novelty and non-obviousness of the invention. The process of obtaining a patent can be time-consuming and expensive, but it

can also provide valuable protection and exclusivity for the inventor's ideas.

Copyright is a form of legal protection provided to creators of original works for authorship, such as litter, dramatic, musical, artistic, and certain other intellectual works. It gives the creator the exclusive right to control the use and distribution of the work for a limited period. Copyright protection applies to works that are fixed in a tangible form of expression, such as a book, a painting, or a software program. The owner of the copyright has the exclusive right to reproduce the work, distribute copies, and create derivative works based on the original. Infringement of copyright can lead to legal action under civil law.

### 1.6 Background on High-Level Synthesis

High-level synthesis (HLS) [2], [5] is the process of automatically translating a high-level hardware description language (HDL) specification into a register-transfer level (RTL) description, which can be used to implement the design on a specific hardware platform. The goal of HLS is to reduce the time and effort required to design complex hardware systems, by allowing designers to describe the system at a higher level of abstraction, and then automatically generate the low-level hardware implementation. HLS has become increasingly important in the field of digital design, as the complexity of modern hardware systems has grown dramatically. The use of HLS can significantly reduce the time-to-market and development costs of such systems, by enabling designers to quickly explore and evaluate a large number of design alternatives, and optimise their designs for different performance metrics such as power consumption, area, and latency.

### **Design Entry Phase:**

The design entry phase is the initial stage of the high-level synthesis process. In this phase, the designer defines the high-level system specification, which consists of the functional behaviour of the system and the constraints on the system's resources. The input to this phase is a high-level language description of the system's behaviour, such as C or MATLAB, and the constraints on the system's resources, such as the area, power, and execution time. The design entry phase begins with the conversion of the high-level language description into a data flow graph (DFG). The DFG represents the data dependencies among the system's operations. Each node in the DFG represents an operation, and the edges represent the data dependencies between the operations. The DFG provides a high-level representation of the system's behaviour.

In addition to the DFG, the designer also creates a control flow graph (CFG) in the design entry phase. The CFG represents the control flow of the system, i.e., the sequence of operations executed by the system. The CFG provides a high-level representation of the system's control behaviour. The designer combines the DFG and CFG into a control/data flow graph (CDGF) in the design entry phase. The CDFG is a unified representation of the system's control and data flow behaviours. The CDFG consists of nodes that represent operations and edges that represent both data and control dependencies.

### High-level design phase

The high-level design phase is a critical stage in the high-level synthesis, where a behavioural description of the system is transformed into an optimised register transfer level (RTL) design. The objective of the high-level design phase is to determine the most efficient way to implement the functionality of the system while satisfying the constraints specified by the user. During this phase, the system is modelled as a set of data flow graphs (DFGs) and control flow graphs (GFGs) that capture the

computational and control aspects of the system. These graphs are used to analyse the system and identify the optimal way to implement the functionality of the system. The high-level design phase can be divided into three main steps: scheduling, resource allocation, and binding.

### Scheduling:

The scheduling step determines the order in which the operations in the DFG will be executed. The goal of scheduling is to minimise the number of clock cycles required to execute the operations while satisfying any timing constraints specified by the user.

#### Resource allocation:

Resource allocation is the process of determining which hardware resources (such as functional units, registers, and buses) will be used to implement the operations in the DFG. The goal of resource allocation is to minimise the overall cost of the system while satisfying any resource constraints specified by the user.

### • Binding:

Binding is the process of assigning each operation in the DFG to a specific hardware resource. The goal of binding is to minimise the critical path delay of the system while satisfying any timing constraints specified by the user.

In addition to these three steps, the high-level design phase may also include optimisation techniques. Optimisation techniques play a crucial role in High-level synthesis (HLS) to improve the quality of the synthesised hardware design. Optimisation techniques help to achieve design objectives such as minimum area, maximum speed, and low power consumption while satirising the constraints and goals of the design. Some of the commonly used optimisation techniques in HLS are:

• **Design Space Exploration (DSE):** DSE is the process of exploring the design space of a system to find an optimal implementation that satisfies

the design objectives such as minimum area, maximum speed, and low power consumption. DSE allows the designer to explore different tradeoffs between design objectives and select the best possible solution.

- Loop unrolling and Pipelining: Loop unrolling is a technique used to improve the performance of a loop by executing multiple iterations of the loop in parallel. Pipelining is another technique used to improve the performance of a design by breaking it down into smaller stages and executing them in parallel. Both techniques help to improve the throughput of a design.

- Data path optimisation: Data path optimisation is the process of optimising the data path of a design to improve its performance. It involves optimising the number and type of functional units used, the number and type of registers used, and the interconnect between the functional units and registers.

- Control path optimisation: Control path optimisation is the process of optimising the control path of a design to improve its performance. It involves optimising the control logic used to generate the control signals that drive the functional units and registers.

- **Power optimisation:** Power optimisation is the process of optimising the power consumption of a design. It involves minimising the dynamic power consumption by reducing the switching activity in the design and minimising the static power consumption by reducing leakage currents.

Overall, the high-level design phase is a critical step in the high-level synthesis that determines the optimal way to implement the functionality of the system while satisfying the constraint specified by the user. By using a combination of scheduling, resource allocation, binding, and optimisation techniques, high-level synthesis tools can produce optimised RTL designs that meet the performance, power, and area requirements of the system.

### RTL generation phase:

RTL (Register Transfer Level) generation is the final phase of the High-level synthesis process where the synthesised hardware design is transformed into an RTL implementation. The RTL implementation is a low-level hardware description that can be used to generate a physical implementation of the design. In this phase, the control and data path structures of the design are synthesised and integrated to produce a complete RTL description. The RTL generation process involves the conversion of the synthesised CDFG (Control/Data flow graph) to RTL-level structural description. The CDFG contains all the information about the design, including the operation, data dependencies, control flow, and resource allocation information. This information is used to generate an RTL description that is compatible with the target technology and the design constraints. The RTL implementation is then verified using simulation and synthesis tools.

The RTL generation process typically involves the following steps:

- 1. **Datapath and Control Path Synthesis:** In this step, the hardware resources such as registers, memories, and arithmetic units required for the design are identified and allocated. The datapath and control path structures are then synthesised by mapping the operations of the CDFG to the hardware resources.

- 2. RTL Netlist Generation: Once the datapath and control path structures are synthesised, an RTL netlist is generated that describes the hardware implementation of the design. The RTL netlist is a structural description of the design that includes information about the hardware components, their connectivity, and the timing constraints.

- 3. **Verification:** The RTL implementation is then verified using simulation and synthesis tools. The simulation is done to verify the correctness of the design functionality and the timing constraints.

- Synthesis tools are used to check the design against the target technology libraries and constraints.

- 4. Optimisation: Finally, the RTL implementation is optimized to improve its performance, power consumption, and area utilisation. Various optimisation techniques such as logic restructuring, clock gating, and retiming are applied to the RTL implementation to improve its efficiency.

The RTL generation phase is a critical step in the High-level synthesis process as it provides a complete hardware implementation of the design that can be used for further verification, testing, and physical implementation. The accuracy and quality of the RTL implementation have a significant impact on the final performance, power consumption, and area utilisation of the design. Therefore, it is important to ensure that the RTL implementation is optimised, verified, and meets all the design requirements before proceeding to the physical implementation phase.

### 1.7 Organisation of the Thesis

This thesis is organised into eight chapters. Chapter 2 describes the related works regarding the proposed approaches, chapter 3 and 4 discusses the proposed quadruple-phase watermarking methodology, chapter 5 and 6 discuss the proposed unified biometrics with an encoded dictionary for hardware security of fault-secured IP core designs, chapter 7 presents the results of the proposed methodologies, demonstrating a significant decrease in the probability of coincidence and a higher level of tamper tolerance compared to previous techniques, without incurring significant design cost overhead. Finally, chapter 8 concludes the thesis, summarising the proposed methodologies' contributions and their impact on the field of IP security in chip designs.

### **Chapter 2**

# Review of Past Work and Problem Formulation

Hardware IP watermarking techniques have been a popular form of IP protection techniques for securing data-intensive hardware coprocessors used in consumer electronics-based industry, but their (earlier approaches) effectiveness depends on various factors such as the type of watermarking technique used, and the potential attacks that the watermarking technique can withstand. Therefore, the development of effective hardware IP watermarking techniques requires a clear understanding of the strengths and limitations of existing techniques and the identification of potential vulnerabilities or attacks that could compromise their effectiveness. In this section, we highlight the need for further research into the development of hardware IP watermarking techniques to enable the effective protection of valuable IP assets in the chip design industry against hardware security threats.

### **Prior works:**

Various hardware security techniques have been proposed for protecting combinational/sequential circuits and complex DSP circuits using IP watermarking. One approach proposed by Cui *et al.* [6] employed a constraint-based watermarking scheme where closed cones are modulated to embed security constraints at the logic level. Another approach by Cui and Chang [7] employed template substitution-based watermarking, where specific cells are replaced with equivalent templates in the library. To protect combinational circuits, watermarking is usually employed during the combination logic synthesis phase of the design process. For securing sequential circuits, a watermarking scheme has been proposed where the output of transitions of the state transition graph is

used to embed signature bits [8]. Cellular automata-based FSM watermarking schemes have also been proposed by Karmakar and Chattopadhyay [9, 10] to secure IP cores. However, these watermarking schemes [6, 7, 8, 9, 10] have been proposed at the combinational/sequential logic synthesis level and do not target the security of complex DSP circuits.

Other watermarking schemes [11-15, 16] have targeted the security of DSP circuits, including an approach proposed by Sengupta and Rathor [16], where a watermark is employed in a DSP circuit during the early floor planning stage at the physical level. Some of the watermarking approaches such as [41], [13] are utilised at the lower levels of abstraction, such as at the gate level. When operating at the gate level, a vendor signature may be incorporated into the design using either (i) the netlist and bit stream of an IP design as proposed in D. Ziener et al. [41], or (ii) during the in-synthesis process of design like approaches by Le Gal and Bossuet [13] implanted during the in-synthesis phase of the HLS process of DSP designs. However, since both of these approaches embed the signature at a lower level, they are not appropriate for complex DSP cores, and the insertion of the signature results in significant overhead on the system. As a result, alternative techniques have been developed that target insertion of the signature at a higher abstraction level such as the architecture level. For instance, a watermarking technique involves implanting a secret mark at algorithmic synthesis, which can be accomplished using various methods, including (i) multi-variable signature encoding rules for IP core protection [15], [42], (ii) multi-variable signature watermarking at three different phases of architectural synthesis (the scheduling phase, the hardware allocation phase, and the register allocation phase). Koushanfar et al. [13] and Hong and Potkonjak [14] embedded signatures during the register binding phase of the HLS process, and Sengupta and Bhadauria [15] secured DSP circuits using a fourvariable signature to embed watermark during the register biding phase of the HLS process. A seven-variable signature embedded during the three phases (scheduling, register binding and FU binding) of HLS was used by Sengupta *et al.* [12], and (iii) encoding the author's signature by adding a set of design and timing constraints to the design [11], [14]. Castillo *et al.* [40] introduced a technique for IP watermarking at the hardware description language (HDL) design level, aimed at safeguarding IP cores. The authors in [40] employed a secure signature extraction methodology integrated with minimal system modification in their approach. In their work, they also utilised a tool to discover diverse input patterns that yield the same output, and this is where the signature block is located. However, these watermarking schemes use a signature that is converted into security constraints using the designer's encoding rules, the goal of watermarking is thwarted when an attacker possesses knowledge of the selected signature and encoding rules.

In addition to the watermarking techniques, an IP core steganography scheme [17] has been proposed that embeds vendors' steno-constraints into the DSP design to secure them against IP piracy. However, these constraints are also replicable by the attacker. The proposed quadruple phase watermarking approach overcomes this limitation by generating a robust author's signature through a novel mechanism of graph partitioning, eight-variable encoding using an encoding tree, and hashing. The signature is embedded during four different phases of the HLS process to achieve high-quality watermarking, with a low probability of coincidence, in contrast to the related approaches of securing DSP circuits. A qualitative comparison of the proposed approach with different existing techniques is presented in chapter 7.

Prior methods used for securing hardware IP cores include IP watermarking [18, 10, 11], [7, 13, 19, 20, 21, 22, 8] stenography [17], [23]

hardware authentication using physically unclonable functions (PUFs) [24], [25] unimodal palmprint biometrics [26], unimodal facial biometrics [27], and unimodal fingerprint biometrics [28]. Rai et al. [18] used a hardware watermarking technique based on polymorphic inverter designs using reconfigurable technologies. Koushanfar et al. [11] presented a hardware watermarking technique that embeds the generated watermark signature into the design. Gal and Bossuet [13] presented an IP watermarking included in high level synthesis based on mathematical relationships between numeric values. Shayan et al. [19] used a watermarking technique inspired by a stealthy hardware trojan. Kuai et al. [20] developed a combined locking and watermark gin technique based on finite-state machines. Kean et al. [21] presented the approach of the embedding watermark by creating specific electromagnetic (EM) information. Becker et al. [22] presented a side-channel-based watermark gin that relies on side-channel information to embed the watermark.

To provide multi-cycle transient fault resiliency at the behavioural level, some authors in [43, 44, 45] have adopted a concurrent error detection (CED) approach. Specifically, they use dual modular redundancy (DMR) logic to duplicate the control data flow graph (CDFG) operations and impose specific hardware allocation rules to provide detection ability. However, the approach presented in [44] differs from that in [43, 45] in terms of advanced resiliency rules. In [43], at least two distinct hardware units are required for assignment to sister operations of the original and duplicate unit in DMR, whereas this is not necessary in [44]. In [44], even a single hardware module of a particular type can provide transient fault resiliency, making the approach more robust and cost-effective. Multiple transient faults have received very little attention because they were rear in past technologies. The focus was only on memory, not hardware modules. However, approaches, such as [46], have focused on multiple transient faults using a simulation-based technique. Specifically, [46] used

simulation to estimate the size of multiple transients resulting from a single radiation strike and their impact on the gate output for different gate input combinations. Furthermore, [47] focused on modelling transient fault propagation once a fault occurs at the gate output inside a logic circuit. The proposed fault-secured design in the unified biometric hardware security approach simultaneously tackles multi-cycle transient and multi-transient fault resiliency at a higher behavioural/architectural level.

Additionally, Sengupta and Rathor [17] presented a steganography approach that generates the steno-mark based on secret design data, encoding rule, and chosen threshold value to be embedded into the design. Rathor and Sengupta [23] presented hardware steganography using switchbased key-driven hash chaining. However, all of these methods are vulnerable to an adversary such as, in the case of watermarking, if an adversary manages to access the decoding combination of encoding digits, signature size, and encoding rule, they can easily replicate and reuse it to evade the IP piracy detection process. Similarly, in the case of steganography, if an adversary manages to decode the entropy threshold, stage keys, and encoding rule, they can also evade IP piracy detection by replicating the stego-mark. The proposed unified biometric driven hardware security methodology, on the other hand, uses a unified biometric-driven encoded signature to incapacitate an adversary, unlike prior works which have only used a secret signature scheme. Moreover, none of the previous methods exploited the expandable encoded dictionary technique on top of unified biometric-driven hardware security methodology to enhance the security of IP cores, unlike the proposed work. Additionally, methods based on PUFs have been suggested by Zalivaka et al. [24] and Lao et al. [25] for the authentication of IP. These methods provide a security primitive for FPGA/system-on-chip bitstream and device authentication. Although these works have demonstrated their efficiency against such devices, they do not focus on the security of DSP cores against IP piracy and false claims of ownership, unlike the proposed methodology.

Sengupta et al. [26, 27, 28] introduced biometric-based methods that use unique biometric features to create a digital signature. For instance, a contact-based high-resolution palmprint image acquisition system is presented in [48], a palmprint feature generation and expatriation using DSP algorithms and principal component analysis is presented in [49], and a multimodal palm biometric system was implemented on FPGA [50]. Furthermore, a high-resolution palmprint authentication system based on the pore feature was presented in [51]. Although these palmprint biometric approaches [48, 49, 50, 51] are used for the identification/ recognition of persons during authentication, however, palmprint biometrics has never been employed for the security of DSP cores so far. Additionally, some approaches like [52] involve cryptography to encrypt palmprint, face and signature images using advanced hill cypher techniques or analyse features present in palmprint and palm vein images using contourlet transform [53]. While cryptographic digital signaturebased techniques (such as those proposed in [54]) are effective, there exist some differences between the proposed unified biometric approaches when compared with cryptographic digital signatures, such as the generation process of cryptographic digital signatures [54] is complex and involves several steps, making it cumbersome. In contrast, the proposed unified biometric approach is simple yet highly secure as they rely on natural biometric features to provide uniqueness and also the encoded expandable dictionary, without the need for complex security-enhancing steps in between and also the process of generating cryptographic digital signatures [54] relies on a casing algorithm that involves multiple intermediate steps to produce a hash or digest. This algorithm requires knowledge and storage of multiple hash buffers and additive constants, as well as complex word computation functions, and round computation functions (including condition, rotation, summation, and majority functions), all of which contribute to the complexity of the process. In contrast, the proposed unified biometrics approach provides uniquely secure constraints with minimal complexity. In the proposed unified biometric approach, in the case of the palmprint approach, the palm image is divided into a specific grid size, and nodal points are created based on the palm features. The final signature is generated by concatenating the palm features. Similarly, the facial biometric approach generates facial nodal points and concatenates them to form the facial signature. The fingerprint biometric approach preprocesses the captured fingerprint impression to extract minutiae points, and then combines the coordinates of minutiae points, crossing number value, and angle magnitude to generate the fingerprint signature. However, these approaches do not provide protection against IP piracy for faultsecured DSP design, unlike the proposed unified biometric approach. Moreover, the proposed unified biometric approach combines palmprint, facial and fingerprint biometrics to create a unified biometrics signature for embedding into the design. Our proposed methodology utilises the expandable encoded dictionary technique to achieve enhanced security. We can tailor the proposed unified biometrics signature to select the biometric signature strength and combination. This offers several times higher security with a lower probability of coincidence and higher tamper tolerance than recent state-of-art approaches. Therefore, our proposed approach provides robust security for fault-secured designs with minimal design cost overhead.

## **Chapter 3**

# Quadruple phase watermarking during high level synthesis for securing reusable hardware intellectual property cores

The watermarking approach is a robust hardware security technique to protect IP cores from hardware threats like IP counterfeiting, cloning, and ownership infringement. Watermarking refers to the process of embedding a unique signature, also known as a watermark, into the design of the IP core. The signature serves as a way to identify the IP core's origin and authenticity and can detect unauthorised copies or modifications. In these watermarking approaches [11, 12, 13, 14, 15] for securing IP cores, the designer or vendor usually determines the signature and its encoding rules. The signature is then transformed into security constraints based on the encoding rules provided. Nevertheless, if the signature and encoding rules are compromised by an adversary, the watermark becomes vulnerable to attacks and can no longer provide the intended level of security against hardware security threats. Given this situation, the adversary can fraudulently claim IP ownership or may try to evade the IP counterfeit detection process. This limitation of watermarking approaches, where the signature can be compromised by an adversary, can be overcome by generating the signature rather than using a signature directly provided by the IP vendor. By using a robust process to generate the signature, the watermark can be made more secure and resistant to attacks, providing a higher level of protection for the IP core and this would hinder the attacker's malicious effort of decoding the signature and claiming it for wrong purposes such as IP piracy and claiming IP ownership.

We proposed a novel watermarking technique for DSP-based IP cores where the signature is generated through a robust process and covertly embedded into the design during the four phases of the high-level synthesis (HLS) process viz. Scheduling, Register Binding, Functional Unit (FU) binding, and Interconnect binding. By embedding the signature into the design during the four phases of the HLS process, the watermark becomes more resistant to attacks and also ensures that the signature is not only present in the design but also deeply ingrained in the internal workings of the IP Core, making it more difficult for an adversary to exactly reproduce the signature.

#### **Threat Model:**

The increasing use of reusable hardware IP cores in IC design flow has made them susceptible to the threats such as IP piracy and fraudulent claim of IP ownership. In the case of IP piracy, an adversary may illegally pirate or imitate the hardware IP core without the knowledge and consent of the original IP vendor or designer [29, 17]. This type of piracy can occur in various scenarios, but one common situation is when a third-party design house is contracted to develop a design on behalf of a client, the client may provide the design house with proprietary information, such as the functional description of the IP core, and expect that the design house will keep the information confidential and use it only for the intended purpose. However, an adversary within the third-party design house may attempt to use the proprietary information for their benefit, such as by copying the design of the IP core and selling it to others without the knowledge or consent of the original IP vendor or designer. This can result in financial losses for the IP vendor or designer, as well as damage to their reputation. In the case of a fraudulent claim of IP ownership, an adversary may unlawfully claim ownership of the intellectual property (IP), despite not having any legal rights to the IP core [11]. For example, an adversary working for a third-party design house could claim ownership of an IP core that they did not create or license, and then use that IP core in the development of a consumer product that competes with the original owner's product. The adversary may be motivated by a desire to profit from the product without having to pay royalties to the true owner of the IP core. Another example of a fraudulent IP ownership claim in the case of an IP core could be a situation where a competitor falsely claims that they own the IP core and sues the true owner for infringement of their IP rights. This type of scenario could result in the true owner of the IP core losing valuable time and resources defending against a frivolous lawsuit, potentially leading to financial losses and damage to their reputation.

A quadruple phase IP watermarking scheme has been proposed to counteract the potential threats of IP piracy and fraudulent claims of IP ownership within the Integrated Circuit (IC) design flow process. By implanting the signature into the IP design during the High-Level Synthesis (HLS) process, the proposed scheme enhances the robustness of the watermark and provides a higher strength of ownership proof and also enhances the tamper tolerance of the watermark by deeply embedding the signature constraints into the IP design during the four phases of the HLS process: scheduling, register binding, functional unit binding, and interconnect binding.

## 3.1 Overview of the proposed approach

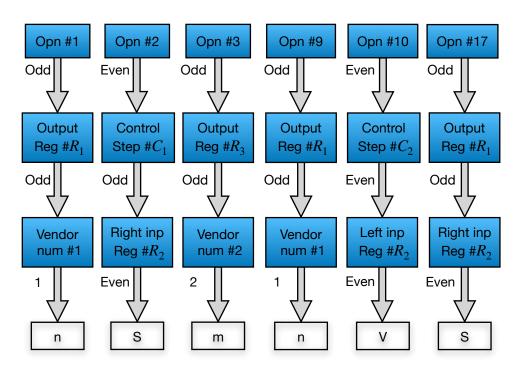

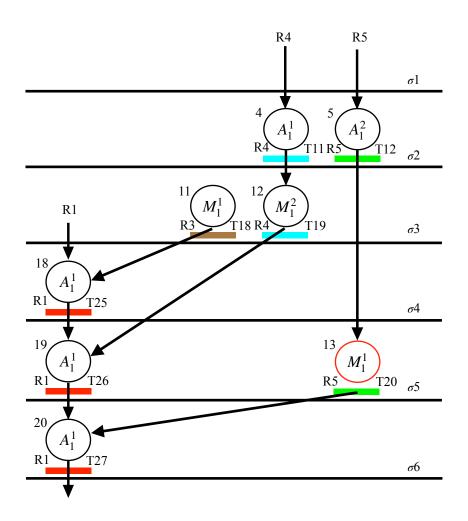

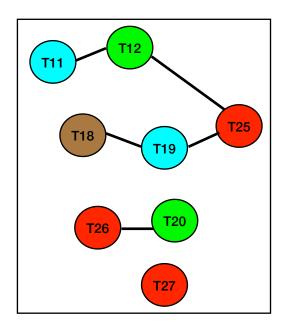

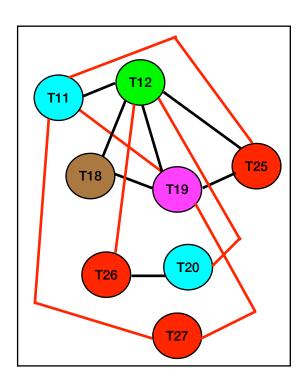

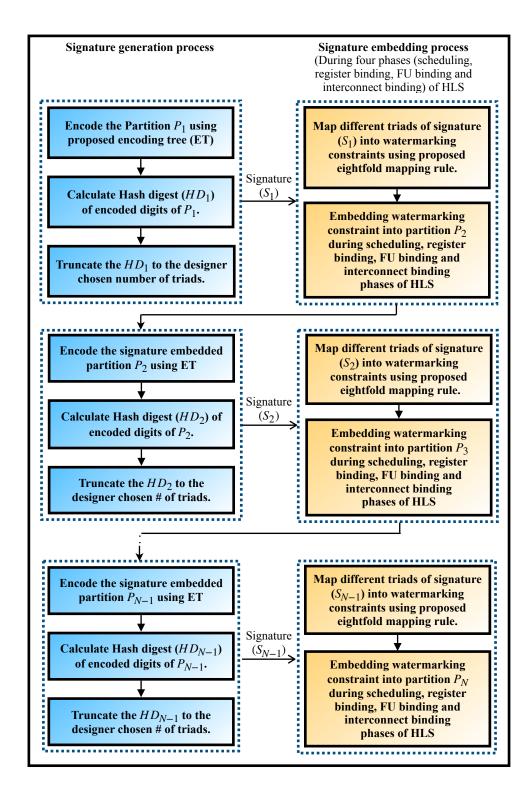

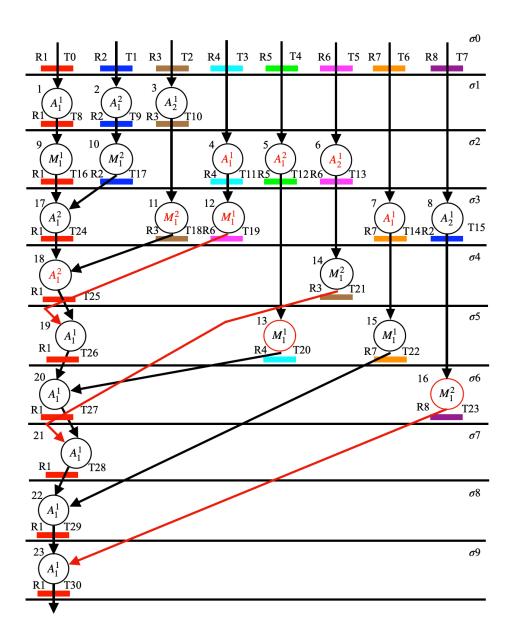

The proposed quadruple phase watermarking approach is outlined in Fig. 3.1. Fig. 3.1 depicts the steps involved in generating and embedding a unique signature into the target DSP application. The proposed approach requires the following inputs such as (i) algorithmic representation of the target DSP application to be secured, (ii) designer-selected encoding tree, (iii) module library, (iv) resource constraints, and (v) mapping rules. Initially as shown in Fig. 3.1, the DSP application's algorithmic

representation is converted into an equivalent form of a data flow graph (DFG). This DFG is then scheduled and resource allocated using resource constraints and a module library provided by the designer. Then, the scheduled and resource-allocated data flow graph (SDFG) is divided into a specified number of partitions, denoted as 'N'. Further, in the proposed watermarking approach, the first partition  $(P_1)$  of the SDFG is encoded to create the signature  $(S_1)$ , which is then embedded into the second partition  $(P_2)$  of the SDFG and later the encoding of the partition  $(P_2)$  with the embedded signature is used to generate the next signature  $(S_2)$  which is then embedded into the next partition  $(P_3)$ . This process is repeated for subsequent partitions of the SDFG. By using this chain-like process, the author's signature is generated and embedded into the design of the provided DSP application. The signature generation and embedding process details are discussed in this chapter and the next chapter respectively. To produce the ith signature from the ith partition of the SDFG, the partition  $P_i$  is converted into alphanumeric characters using the proposed encoding tree (ET). Later, these alphanumeric characters are given as input to the SHA-512 algorithm to generate the corresponding hash digest  $(HD_i)$ . The resulting 512-bit hash is then truncated to the designer-specified size of the bitstream, which is used to create the signature  $S_i$ . The truncated bitstream is represented as 3-bit triads, with each triad representing a single digit in the author's signature. Using the combination of triads in the signature, each triad is mapped to its corresponding security (watermarking) constraints using the proposed eightfold mapping. This mapping allows the signature to be embedded into the design in such a way that it will be difficult to remove or modify the watermarking constraints without impacting the functionality of the design. The proposed mapping rules map signature triads (or signature digits) into four types of design constraints viz. scheduling, register binding, FU binding and interconnect binding. The constraints that correspond to the ith signature are embedded into the (i+1)th partition of the SDFG during four

Fig. 3.1 Flow diagram of proposed quadruple phase watermarking approach

phases of the High-Level Synthesis (HLS) design process. This process is repeated for all signature segments up to  $S_{N-1}$ , which is embedded into the Nth partition of the SDFG. After embedding the entire signature into the design during the HLS process, the datapath synthesis phase is executed to generate the Register Transfer Level (RTL) datapath with the embedded watermark.

The details of the proposed watermarking scheme are divided into two parts as shown in Fig. 3.2, the signature generation phase and the signature embedding phase. The signature generation phase will be discussed in this chapter and the signature embedding phase will be discussed in the next chapter.

Fig. 3.2 Abstract view of the proposed quadruple phase watermarking approach

The proposed quadruple phase watermarking approach is explained thoroughly and demonstrated using an 8-point Finite Impulse Response (FIR) core in separate subsections. The demonstration of the watermarking

scheme on the FIR core serves to illustrate how the watermarking process can be applied to a specific design, providing a clear and tangible example of each step involved in the process. This approach helps to offer a more comprehensive and practical understanding of the proposed watermarking scheme.

# 3.2 Partitioning of Scheduled Data Flow Graph (SDGF)

In the proposed watermarking approach, an author's signature is generated by encoding a specific partition of the SDFG, referred to as the "ith" partition. The signature is then inserted into the next partition, which is the "(i+1)th" partition of the SDFG. The process is repeated for all partitions, with "i" varying from 1 to "N-1", where "N" represents the total number of partitions in the SDFG. For the partitioning of SDFG to be effective in watermarking, certain requirements must be satisfied, such as (i) the smallest possible partition should contain at least two connected nodes of the graph to facilitate more meaningful encoding and embedding of constraints, (ii) there should be a minimum of two partitions of the graph for the proposed approach to be applicable, (iii) the first partition  $P_1$ should be the smallest, as the constraints are not embedded in this partition, but it is used to derive the signature for the subsequent partition, and finally (iv) the number of partitions should vary based on the size of the target application (in terms of the number of operations) to enable effective watermarking. It is important to note that the partitioning of the Scheduled Data Flow Graph (SDFG) is not in any way linked to the circuit partitioning. The motivation behind the partitioning of SDFG is to improve the robustness of watermarking.

The proposed method of partitioning the scheduled data flow graph plays a significant role in augmenting the strength of the signature. As a result of the partitioning, the complexity of determining the exact signature is increased by a significant factor for an attacker, this is because an attacker would require the knowledge of the partition location, the total number of partitions of the SDFG, and the partition encoding to deduce the signature. In addition, the partition of the graph containing the embedded signature also participates in generating the next signature. This process makes the generated watermarking constraints highly robust, and it becomes challenging for an attacker to decode it.