## Chapter 04

Integrating Multi-key based Structural Obfuscation and Low-level Watermarking for Double Line of Defence of DSP Hardware Accelerators

Anirban Sengupta Computer Science and Engineering Indian Institute of Technology Indore

The chapter describes a double line of defense mechanism for securing hardware accelerators using key-based structural obfuscation and physical level watermarking. The presented approach discussed in this chapter is capable of securing against combined threat models of reverse engineering (leading to Trojan insertion) and IP piracy as preventive and detective control. The chapter is organized as follows: Section 4.1 discusses about the background of the chapter; Section 4.2 presents the salient features of the chapter. Section 4.3 shows some practical applications applicable for this approach; Section 4.4 explains some contemporary approaches of this domain; Section 4.5 explains the details of the double line of defense process; Section 4.6 highlights the low-cost optimized multi-key based structural obfuscation process; Section 4.7 presents the KSO-PW tool of the presented approach; Section 4.8 discusses the case studies on DSP applications and Section 4.9 concludes the chapter.

## 4.1. Introduction

In this era of consumer electronics, digital signal processing (DSP) hardware accelerators have begun to dominate because of its vital role in image processing, audio processing, video processing and so forth applications. Today, nobody wants to compromise with the rate of video streaming and quality of videos. Moreover, high quality audio such 8-dimensional (D) audio are fascinating the consumers today. Various kinds of image filters have set their role in applications such robotics vision, biometric fingerprinting and medical imagery etc. Therefore the proliferating demand of high definition (HD) video, high quality audio and various kind of image filtering are the key reasons for blooming of DSP hardware accelerators in modern consumer electronics era. Apart from consumer's applications, the utility of DSP hardware accelerators is well pronounced in several critical applications such as military, banking and healthcare etc. (Schneiderman, 2010; Sengupta, 2020).

So far we have discussed only application side of the DSP hardware accelerators. However, another side of DSP hardware accelerators is its design-for-security (DFS) that is also being given strong attention by industry and researchers today. The DFS perspective of a DSP hardware accelerator is vital for its usage in both critical and non-critical applications. This is because

ensuring a secured design of DSP hardware accelerators builds up trust in hardware. This chapter focuses on design for security (DFS) perspective of DSP hardware accelerators. Now the question arises as to why the DFS is prevailing in modern system-on-chip (SoC) design technology. The key reason is the distribution of deign chain across the globe. In other words, various offshore entities (fabless design houses, SoC integrators and foundries) participate in the journey of an electronics system from its idea to physical existence (Sengupta, 2016; Sengupta, 2017; Plaza and Markov, 2015; Castillo *et al.*, 2007). During this journey, a DSP hardware accelerator design can be infected with malicious logic insertion by any untrustworthy design house involved in the design process (Zhang and Tehranipoor, 2011). For example, (i) a dishonest third party intellectual property (3PIP) vendor may covertly insert a Trojan horse at a safer place in the design and send Trojan infected IPs to the SoC integrator (ii) a dishonest SoC integrator may covertly insert a Trojan horse before sending the design to the fabrication unit or foundry (iii) an adversary in fabrication unit may insert the Trojan in the mask or by altering the dopant level. Thereby, a DSP hardware accelerator design can be compromised by an attacker using Trojan horse attack. This may lead to failure of hardware accelerators deployed in critical systems. Apart from Trojan threat, other threats such as counterfeiting and cloning are also becoming a challenge for trustworthy hardware designs (Sengupta *et al.*, 2019; Sengupta and Rathor, 2019a). This is because the economic temptation and intents of sabotaging the genuine vendor's reputation and revenue may push an adversary (untrusted entity in the design chain) towards counterfeiting and cloning of hardware designs (Sengupta and Roy, 2017; Sengupta and Mohanty, 2019).

The above discussion is the underlying reason of the ramification of the very large scale integration (VLSI) design process in the form of design-for-security (DFS). The DFS can be performed at various phases of design process viz. high (behavioural) level, register transfer level (RTL), gate level and physical/layout level. This chapter highlights on how a high level and the low level (physical level) can simultaneous be exploited to employ security against Trojan insertion, counterfeiting and cloning threats (Sengupta and Rathor, 2020). The design-for-security (DFS) at both high level and low level strengthens the trust in hardware designs. (Sengupta and Rathor, 2020) performed the high level DFS by employing multi-key based structural obfuscation during high level synthesis. Further, low level DFS has been performed by embedding watermarking at physical level. Thereby, (Sengupta and Rathor, 2020) integrated structural obfuscation at high level and watermarking at low level to provide double line of defence for securing DSP hardware accelerators against Trojan insertion, counterfeiting and cloning threats. The structural obfuscation (Sengupta *et al.*, 2017) based security during the high level design process ensures preventive control against Trojan insertion, counterfeiting and cloning threats. This is because to insert a Trojan horse or to counterfeit and clone the designs, an adversary performs reverse engineering (RE) to deduce the original structure and functionality of the design. On successful RE, an adversary becomes competent to insert malicious Trojan horse or counterfeit/clone the design. However, structural obfuscation alters the design structure in such a way that the RE becomes highly obscure for the attacker. Thus the structural obfuscation

technique obstructs the reverse engineering performed by an adversary and provides security against Trojan insertion, counterfeiting and cloning threats. Further, the watermarking based security during the low level (physical level) design process ensures detective control against counterfeiting and cloning threats. This is because a robust watermark embedded into the designs enables detection of counterfeiting and cloning.

## 4.2. Salient Features of the Chapter

The chapter discusses the security of DSP hardware accelerators based on following key-points (Sengupta and Rathor, 2020):

- Discussion on design-for-security technique to generate highly secured DSP hardware accelerators using double line of defence against Trojan insertion, counterfeiting and cloning threats.

- Discussion on 1<sup>st</sup> line of defence using multi-key driven robust structural obfuscation, as preventive control against aforementioned hardware threats.

- Discussion on obfuscation process using following high level structural transformations which are executed sequentially: (i) key-driven loop unrolling (ii) key-driven partitioning (iii) key-driven redundant operation elimination (ROE) (iv) key-driven tree height transformation (THT) (v) key-driven folding knob based transformation.

- Discussion on 2<sup>nd</sup> line of defence using physical-level watermarking during early floorplanning of obfuscated DSP design.

The watermark depends on vendor's signature comprising of multiple variables, where each variable carries a robust mapping for conversion into respective watermarking constraints. The watermark insertion is overhead free regardless of the size of DSP design.

#### 4.3. Some Practical Applications of DSP Hardware Accelerators for Modern Electronic Systems

In modern electronic systems such as television, digital camera, tablets, headsets, cell phones, laptops etc., DSP hardware accelerators have numerous practical applications. These applications of DSP hardware accelerators include filtering of digital data, attenuation, compression and decompression, audio and video encoding/decoding, speech recognition and so forth (Sengupta and Rathor, 2020). To facilitate these applications, DSP algorithms such as finite impulse response (FIR) filter, infinite impulse response (IIR) filter, discrete Fourier transform (DFT), fast Fourier transform (FFT), discrete wavelet transform (DWT), auto-regressive filter (ARF), discrete cosine transform (DCT), inverse discrete cosine transform (IDCT) etc. are executed as core functions. Because of data-intensive computations involved in theses DSP algorithms, it is efficient to realize them using hardware. Thereby DSP hardware accelerators are designed as dedicated processors such as application specific integrated circuits (ASICs) or reconfigurable logics in programmable devices such as field programmable gate array (FPGA) to execute data-

intensive applications so that high performance can be achieved. Each kind of DSP hardware accelerator performs a specific function such as FIR filter core is used for signal attenuation, image processing, DCT core is used for transforming data from spatial to frequency domain during image compression, IDCT is used for transforming data from frequency to spatial domain during image de-compression, FFT core is used for fast transformation of data from time/spatial to frequency domain for image enhancement (e.g. biometric fingerprint image enhancement), DWT core is used for de-noising, data compression and feature extraction etc. Thus because of wide utility of DSP hardware accelerators, their demand in consumer electronics applications is proliferating.

## 4.4. Overview of Contemporary Approaches

This section discusses overview of contemporary approaches in two parts. The first part of the discussion includes structural obfuscation based contemporary approaches and the second part includes watermarking based contemporary approaches. The discussions on both parts are as follows (Sengupta and Rathor, 2020):

The structural obfuscation based approaches have been proposed for securing both sequential and combinational kind of circuits. For securing sequential circuits against piracy, structural transformation based obfuscation has been proposed by Li and Zhou, 2013. The authors performed following four operations to achieve best-possible obfuscation: (i) retiming (ii) re-synthesis (iii) sweep (iv) conditional stuttering. Further, (Chakraborty and Bhunia, 2009; Chakraborty and Bhunia, 2011) proposed obfuscation techniques to ensure security of designs against Trojan horse insertion. However, these approaches have not been proposed for securing larger designs such as DSP hardware accelerators. Their application is limited to small combinational and sequential circuits. Since their target hardware is not designed using high level synthesis (HLS) framework, therefore the DFS at high level is not possible. However, there are some other approaches which perform structural obfuscation for performing DFS at high level. For example, Lao and Parhi, 2015 performed structural obfuscation based DFS by applying folding transformation on the iterative data flow graph (DFG) of digital filters such as FIR. Further, Sengupta et al., 2017 also performed structural obfuscation based DFS technique at high level using following transformations: loop unrolling (LU), logic transformation (LT), tree height transformation (THT), redundant operation elimination (ROE), and loop invariant code motion (LICM). This technique (Sengupta et al., 2017) targets the security of DSP cores. Further, Sengupta et al., 2018 targeted security of multi-media hardware accelerators such as joint photographic experts group (JPEG) compression processor for securing using THT based structural obfuscation. Further, Sengupta and Rathor, 2019b performed hologram motivated structural obfuscation by concealing one DSP architecture into another. In contrast to theses contemporary approaches, the structural obfuscation based DFS approach to be discussed in this chapter has following enhancements (Sengupta and Rathor, 2020): (i) multiple techniques of structural transformations have been performed (ii) all the applied techniques of structural transformations are driven through a designer's chosen key value, therefore resulting into higher control over the extent to which obfuscation can be applied (iii) an attacker requires to know both the correct keys and the employed multiple techniques of obfuscation to expose the true functionality of the design, hence resulting into higher security against RE attack (iv) applicability on both iterative and non-iterative algorithms of DSP (v) key-driven partitioning and key-driven folding-knob based transformation along with key-driven loop unrolling, key-driven ROE and key-driven THT based structural transformations.

To enable detection of counterfeiting and cloning, some watermarking based contemporary approaches have been proposed for DSP hardware accelerators. For example, Hong and Potkonjak, 1999 proposed watermarking technique based on binary encoding of author's signature. Further, Le Gal and Bossuet, 2012 proposed an In-synthesis watermarking technique which embeds authors signature as output marks. Furthermore, Sengupta and Bhadauria, 2016 proposed watermarking technique based on four variables author signature and Sengupta *et al.*, 2018 proposed watermarking technique based on seven variables author signature. Roy and Sengupta, 2019 proposed a watermark which is embedded at multiple levels of design abstraction such as high level and RTL. However in contrast to theses contemporary approaches, the low level watermarking to be discussed in this chapter has following

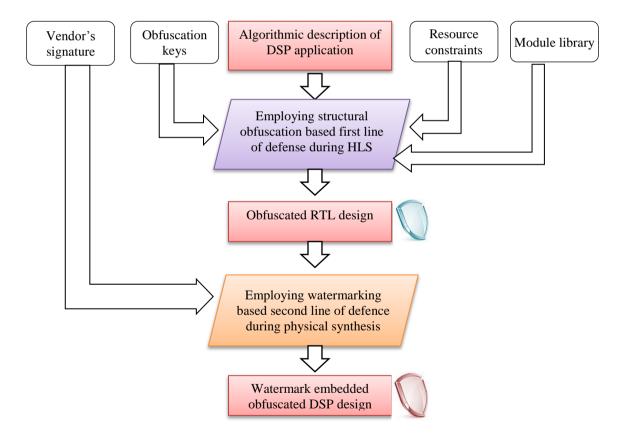

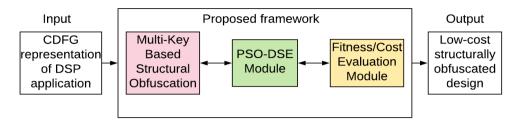

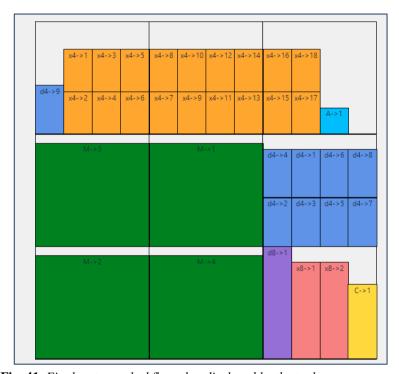

**Fig. 1.** Overview of multi-key based structural obfuscation and physical level watermarking based double line of defense (Sengupta and Rathor, 2020)

differences (Sengupta and Rathor, 2020): (i) the low level watermarking proposed by Sengupta and Rathor, 2020 is embedded during floorplanning at physical level (ii) the author signature comprises of three distinct variables  $\alpha$ ,  $\beta$  and  $\gamma$ , where each variable has a robust mapping into watermarking constraints (iii) the embedding of watermark does not result into design cost overhead (iv) the physical level watermark to be discussed in this chapter has been embedded as a second line of defence, where first line of defence is employed using structural obfuscation. The physical level watermark as a second line of defence offers detective control in case the first line of defence is compromised. More explicitly, if an adversary nullifies the structural obfuscation by deducing the original functionality of an obfuscated design through RE then the physical level watermark acts as a second line of defence. Therefore if the attacker counterfeits or clones the design post compromising the structural obfuscation based security, then the physical level watermark based security helps in detecting counterfeiting and cloning.

## 4.5. Double Line of Defence using Structural Obfuscation and Physical Level Watermarking

Authors (Sengupta and Rathor, 2020) integrated structural obfuscation and physical level watermarking together to secure DSP hardware accelerators using double line of defence.

## 1. Top Down Perspective of the Approach

An abstract view of the structural obfuscation and physical level watermarking based double line of defence process is shown in Fig. 1. As shown in the figure, following inputs are required to generate a watermark implanted obfuscated DSP hardware accelerator as output (Sengupta and Rathor, 2020):

- (i) Algorithmic description of a DSP application in the form of C/C++ or transfer function or mathematical relationship of inputs and output.

- (ii) Resource constraints

- (iii) Module library

- (iv) Structural obfuscation (SO) secret keys (SO-key1, SO-key2, SO-key3, SO-key4, SO-key5)

- (v) Vendor's multi-variable signature comprising of three variables viz.  $\alpha$ ,  $\beta$  and  $\gamma$ .

As shown in the Fig. 1, structural obfuscation based first line of defence is employed during HLS process and requires algorithmic description of the DSP application, resource constraints, module library and structural obfuscation keys, as inputs. After employing the first line of defence, a structurally obfuscated RTL design is generated post-HLS. Thus obtained structurally obfuscated RTL design is fed as input along with the vendor's signature to the second line of defence algorithm. The second line of defence algorithm is performed using watermarking based physical level synthesis. Post-watermarking, a watermark implanted

obfuscated design is generated which is secured using double line of defence. The motivation of employing the double line of

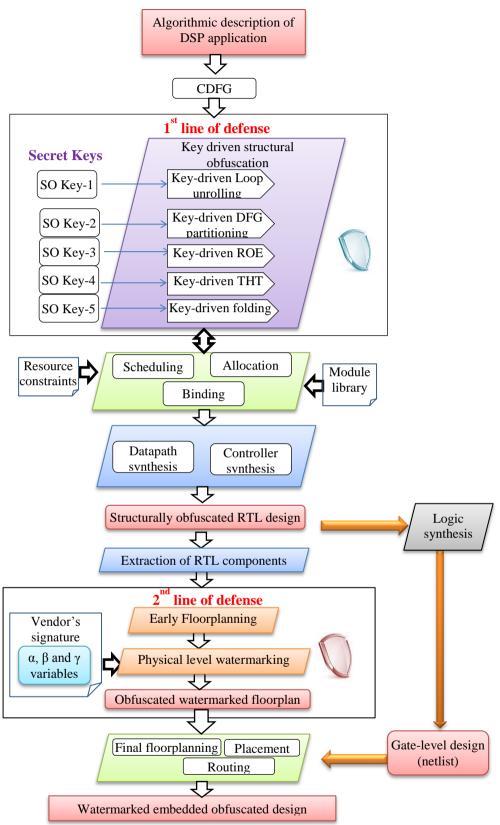

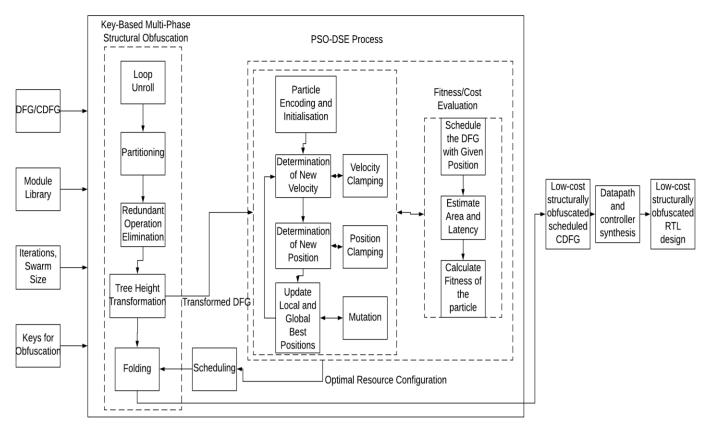

Fig. 2. Secured design flow based on double line of defense approach (Sengupta and Rathor, 2020)

defence is to secure DSP hardware accelerators against following threat scenarios: (i) Firstly, the Trojan insertion threat (resulting from reverse engineering) infecting third party IP cores (3PIP), which in turn compromises the security of SoC design. The first line of defence using structural obfuscation provides security against Trojan which can possibly be inserted in an untrustworthy regime such as foundry (ii) Secondly, counterfeiting/cloning threats that result into integration of fake designs or IP cores into SoC, hence compromising the security and reliability of an electronics system. The first and second line of defence ensures security against counterfeiting/cloning, where multiple SO-keys based structural obfuscation provides preventive control while physical level watermarking offers detective control. The second line of defence is not directly contextual unless the first line of defence is overtaken by an adversary. However somehow if an attacker de-obfuscates the obfuscated design and finds the correct functionality, only then doors are open for him/her for realizing malicious objectives of counterfeiting/cloning. In such a threat scenario, watermarking based 2nd line of defence secures the designs by enabling detective control over counterfeiting/ cloning. A more informative secured design flow of the structural obfuscation and watermarking based double line of defence technique is shown in Fig. 2. As shown in the figure, the algorithmic description of DSP application is first represented in the form of control data flow graph (CDFG). Further, the CDFG is subjected to multiple secret SO-keys based structural obfuscations technique which performs following high level structural transformations (i) key-driven loop unrolling (LU) (ii) key-driven partitioning of CDFG (iii) key-driven ROE (iv) key-driven THT (v) key-driven folding knob based transformation. Post employing these multiple key-driven techniques, the CDFG is transformed in an obfuscated form. This transformed CDFG is subjected to scheduling, allocation and binding phases of HLS to generate an obfuscated design in the form of scheduled and allocated CDFG. Further, datapath and controller are synthesized to generate an obfuscated RTL circuit as shown in Fig. 2. Thus multiple secret SO-keys based structural obfuscation based first line of defence is employed. Now let's discuss how structural obfuscation

When a SoC or a standalone IC design is sent to an offshore foundry for fabrication, the design to be fabricated can be infected with Trojan (malicious logic) or it can be counterfeited/cloned. In order to insert a Trojan, or counterfeit /clone a design, an adversary first tries to interpret the true functionality and structure of design. To do so, the adversary performs RE. Once s/he successfully interprets the true functionality through RE, s/he can easily insert Trojan at safer places inside the design. The Trojan is inserted such that they remain dormant until the payload is activated by the trigger logic. The triggering is designed to occur only at rare events so that the Trojan logic cannot be detected typically during pre and post silicon simulation/validation. Therefore in order to evade detection of Trojan during validation, they are inserted at safe places in the design by an adversary. The insertion of Trojan at safe places in the design is only possible when an adversary successfully interprets the original functionality/structure of the design. Further once the functionality of design is known to the adversary, counterfeiting or cloning

prevents RE which may result into Trojan insertion, counterfeiting/cloning.

can be also executed. The structural obfuscation falls under the preventive control based DFS technique against Trojan insertion and piracy. This is because structural obfuscation aims to modify the design to such an extent that RE becomes arduous for an attacker to perform. Hence, the structural obfuscation technique thwarts RE and provides preventive control against Trojan insertion and piracy. The multiple SO-keys based structural obfuscation incurs very high amount of obscurity into the generated RTL/gate-level design structure (post-HLS) in terms of following modifications, without affecting functionality:

- (i) Changes in the number of functional unit resources (such as multipliers, adders and subtractors) post obfuscation.

- (ii) Changes in the interconnect-hardware (such as multiplexers and demultiplexers) in terms of their size and total count.

- (iii) Changes in the total count of storage resources such as registers and latches.

- (iv) Changes in the inter-connectivity of hardware resources.

So far, we have seen how structural obfuscation based first line of defence thwarts Trojan attack and piracy. Now let's move ahead in the double line of defence based secured design flow of hardware accelerators as shown in Fig. 2. As shown in the figure, a structurally obfuscated RTL datapath is generated post employing the first line of defence. Further in order to employ the second line of defence, firstly a set of RTL components is extracted from the structurally obfuscated RTL datapath. This set of RTL components is used to perform physical level watermarking. The watermarking is employed by performing a physical level design step referred as *early floorplanning* (proposed by Sengupta and Rathor, 2020). The early floorplanning is performed using the set of extracted RTL components. In other words, an early floorplan of RTL components is prepared. Further, this early floorplan is subjected to watermarking based on vendor's signature. The vendor's signature is a combination of three unique variables ( $\alpha$ ,  $\beta$  and  $\gamma$ ), where mapping rules of each variable converts the signature into respective watermarking constraints or hardware security constraints. The watermarking constraints are implanted into the early floorplan of the design, thus resulting into an obfuscated watermarked floorplan. Further the obfuscated watermarked floorplan is subjected to final floorplanning, placement and routing phases of physical synthesis to obtain an obfuscated and watermarked layout file. The final floorplanning, placement and routing phases require gate-level netlist which is generated from logic synthesis of obfuscated RTL design. The embedded watermark in the early floorplan step (proposed by Sengupta and Rathor, 2020) of physical design flow enables detection against piracy/fake designs, hence acts as detective control as double line of defence.

## 2. Details of Double Line of Defence

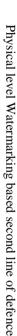

As discussed earlier, double line of defence for DSP hardware accelerators has been deployed by integrating multiple SO-keys based structural obfuscation as a first line of defence and physical level watermarking as a second line of defence. This subsection discusses the double line of defence mechanism in details. The flow chart of the double line of defence process is shown

Fig. 3. Flow chart of the structural obfuscation and watermarking based double line of defence approach for securing DSP hardware accelerators (Sengupta and Rathor, 2020)

in Fig. 3. As shown in the flow chart, the entire flow has been divided into two portions where the first portion depicts the flow of

employing multiple SO-keys based structural obfuscation, as a first line of defence while the second portion shows the physical level watermarking, as a second line of defence. The detailed discussion of the approach with demonstration on DSP cores are given as follows (Sengupta and Rathor, 2020):

## (a) Multiple SO-keys driven structural transformation based obfuscation- the first line of defence

The multiple SO-keys driven structural transformation based obfuscation requires following inputs: algorithmic description of

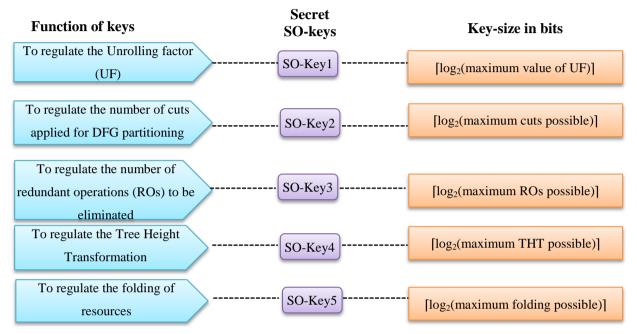

Fig. 4. Functions and Size of each SO-key used in structural obfuscation based first line of defence (Sengupta and Rathor, 2020)

DSP application, multiple structural obfuscation secret keys (SO-key1 to SO-key5), module library and designer's specified resource constraints. As shown in the flow chart in Fig. 3, the process starts with the conversion of algorithmic description of DSP application into its CDFG representation. Further, multiple high level transformations are performed on CDFG in order to obtain a structurally transformed design leading to its equivalent structurally obfuscated design. Each high level transformation technique is driven through a designer's chosen secret SO-key which tailors the extent to which obfuscation has to be performed. Moreover, involvement of multiple secret keys in the structural obfuscation process renders the back engineering of the obfuscated design more complicated by an adversary who is assumed to be associated with an untrustworthy foundry. The function of five secret SO-keys and their sizes are shown in Fig. 4. Now let's see about each key-driven high level transformation based structural transformation/obfuscation technique one by one.

#### (i) Key-driven loop-unrolling based structural transformation

Loop unrolling is a high level transformation technique where loop body of an iterative DSP application is unrolled in order to incorporate parallelism in execution. The unrolling of loop body can be exploited to result into a structural transformation

based obfuscation design. This is because upon loop unrolling, at circuit implementation level (RTL/gate level), the functional unit (FU) resource count, the inter-connect hardware resource (such as multiplexers and demultiplexers) count, storage elements (latches and registers) resource count change drastically. This leads to huge variations in the structure without changing the functionality. Hence, this transformation impedes the deduction of true structure and functionality of the design through RE by an attacker. The extent to which the loop unrolling has to be performed is regulated by a loop unrolling factor (UF).

The loop-unrolling based structural transformation employed by (Sengupta and Rathor, 2020) is driven by secret SO-key1

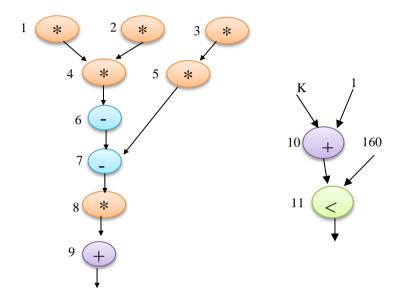

Fig. 5. DFG of differential equation solver

which acts as selected unrolling factor. Therefore, the SO-key1 size depends on the maximum value of unrolling factor. The maximum value of UF is chosen same as the maximum number of iterations (K) in a loop of DSP algorithm. For example, the maximum number of iterations in a 160-tap FIR filter is K=160. The SO-key1 size in bits is shown in Fig. 4.

A demonstration of loop-unrolling based transformation is shown using a loop based DSP application named 'differential equation solver'. The DFG of differential equation solver is shown in Fig. 5, where total number of iteration is assumed to be 160. The loop unrolling based transformation is performed based on designer's chosen secret value of SO-key1. Since K=160, therefore maximum UF value is also equal to 160. Hence the SO-key1 size is calculated to be  $\lceil \log_2(160) \rceil = 8$  bits. For a designer's chosen secret value of SO-key1= "00000100", the UF value to be used for loop unrolling is 4 (which is a decimal equivalent of "00000100"). For UF value equal to 4, the loop unrolled graph of differential equation solver application is shown in Fig. 6. As shown in the figure, the loop body of differential equation solver algorithm has been unrolled four times. This increases the total number of operation in the application nearly four times. This leads to more

Fig. 6. Loop unrolled DFG of differential equation after unrolling with UF=4

utilization of FU resources, multiplexers, demultiplexers and registers. Hence, a drastic variation in RTL structure is incurred which results into structural obfuscation. This is how the first technique of structural transformation based obfuscation is performed.

#### (ii) Key-driven CDFG partitioning based structural transformation

CDFG partitioning is a high level transformation technique which can be exploited in such a way that an unrolled CDFG (in case of iterative DSP application) is partitioned in order to yield structural transformation based obfuscation. The impact of CDFG partitioning for structural obfuscation manifests in the RTL datapath in the form of modified interconnectivity of FU resources and modified size and number of multiplexers and demultiplexers. However, these modifications in the design do not impact any change in the functionality. Each partition of CDFG is further subjected to remaining structural transformation techniques in order to enhance obscurity.

The CDFG partitioning based structural transformation employed by (Sengupta and Rathor, 2020) is driven through designer's chosen secret SO-key2. The value of the chosen key determines the number of cuts to be performed on the CDFG in order to partition the graph; upon performing 'C' number of cuts, the target CDFG is partitioned into 'C+1' number of partitions. The way of applying cuts is again designer's selected. One of the ways that was used by (Sengupta and Rathor, 2020), is that the applied cuts should lead to such partitions where smallest one should comprise of minimum two nodes/operations bearing a data dependency (even if partitions are of unequal size). Thus, the size of secret SO-key2 depends on the maximum number of cuts that can be performed on CDFG. The function and size of SO-key2 is highlighted in Fig. 4.

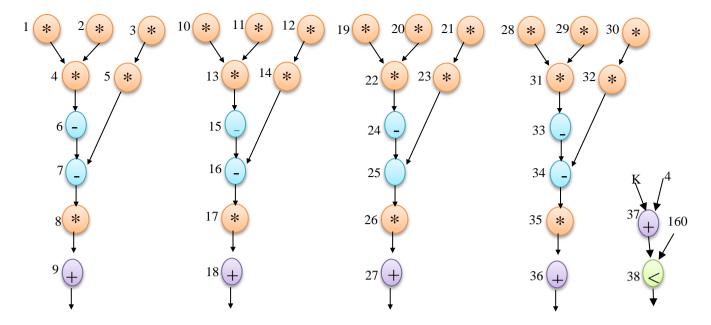

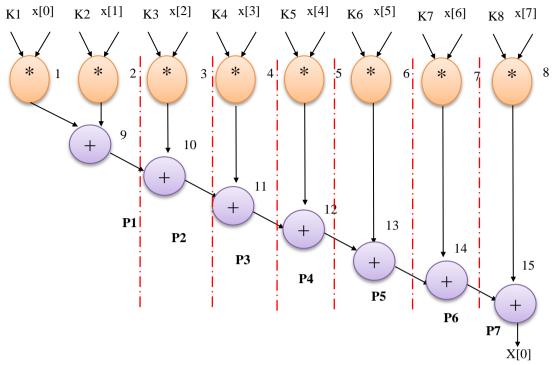

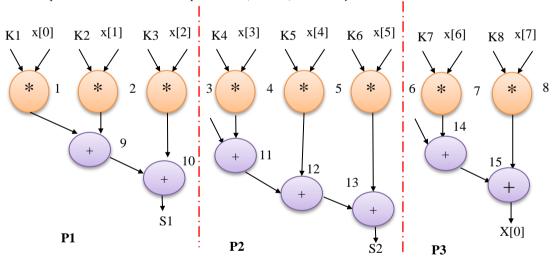

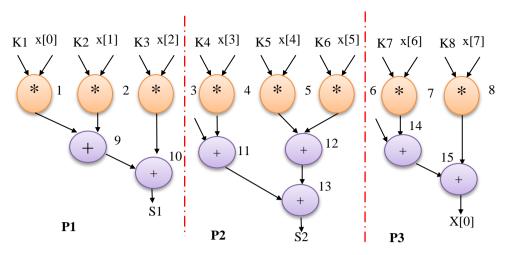

A demonstration of CDFG partitioning based transformation is shown using a DSP application named '8-point discrete

**Fig. 7.** DFG of 8-point DCT core showing maximum 6 cuts can be possible with minimum two nodes in each partition. Due to 6 cuts, 7 partitions (P1-P7) could be yielded.

Fig. 8. Partitioned DFG of 8-point DCT core

Note: Red dotted lines show the cuts applied in partitioning

cosine transform (DCT)'. The generic equation of 8-point DCT is as follows:

$$X[0] = K1*x[0] + K2*x[1] + K3*x[2] + K4*x[3] + K5*x[4] + K6*x[5] + K7*x[6] + K8*x[7]$$

(1)

Where, K1-K8 denote DCT coefficients, x[0]-x[7] indicate input values and X[0] indicates the 1st output sample of 8-point DCT. The corresponding DFG representation of 8-point DCT core is shown in Fig. 7. The DFG partitioning based transformation is performed based on designer's chosen secret value of SO-key2. Maximum six cuts can be applied to generate smallest possible partitions complying with the condition that there should be minimum two operations with data dependency in each partition. Therefore the size of SO-key2 is calculated to be  $\lceil \log_2(6) \rceil = 3$  bits. For a designer's chosen value of SO-key2= "010", the number of cuts to be applied are 2 (which is a decimal equivalent of "010"). The DFG of 8-point DCT on applying C=2 cuts is shown in Fig. 7. Post applying two cuts, resultant three partitions P1, P2 and P3 are

Fig. 9. DFG of ARF application

shown in Fig. 8. As shown in the figure, partitioning alters the interconnectivity of resources which leads to change in the size and number of interconnect hardware resources post behavioural synthesis, without affecting functionality.

## (iii) Key-driven ROE based structural transformation

Redundant operation elimination (ROE) is a high level transformation technique that can be exploited to achieve structural obfuscation. Here such nodes or operations which generate same output because of having same inputs and same operation type are eliminated from the CDFG, in order to achieve structural transformation which in turn yields obfuscated design. To do so, firstly those operations are identified as redundant operations which have their inputs and operation type equivalent with another available node in the CDFG. Next the identified redundant nodes are removed without affecting the design function. The ROE based high level transformation technique contributes in structural obfuscation by incurring the following modifications in the RTL datapath while preserving functionality: modification in the interconnectivity of FU resources and size of multiplexers and demultiplexers.

Fig. 10. Partitioned DFG of ARF application

The ROE based structural transformation employed by (Sengupta and Rathor, 2020) is driven through designer's chosen secret SO-key3. The value of the chosen key determines the number of redundant nodes that have to be removed from the partitioned CDFG. The size of SO-key3 depends on the maximum number of redundant nodes that have been identified across all the CDFG partitions. The function and size of SO-key3 is highlighted in Fig. 4.

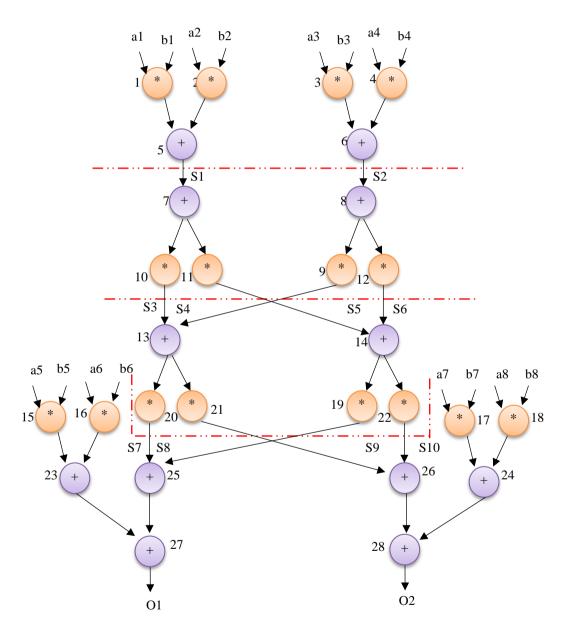

The ROE based transformation cannot be applied on 8-point DCT core as redundant nodes are not present in the corresponding DFG partitions. Therefore, a demonstration of ROE based transformation is shown using auto-regressive filter (ARF) application. The DFG representation of ARF is shown in Fig. 9. The applied three cuts to generate its four partitions are also shown in Fig. 9. The resultant partitions P1, P2, P3 and P4 are shown in Fig. 10. The ROE based structural transformation is performed on the partitioned CDFG based on designer's chosen value of SO-key3. As shown in the partitioned DFG of ARF, there are total maximum four redundant nodes across the partitions. For a designer's chosen value

Fig. 11. Partitioned DFG after ROE based transformation

of SO-key3= "100", the number of operations to be eliminated are 4 (which is a decimal equivalent of "100"). As shown in Fig. 10, operation number 11 and 12 are redundant in partition P2 as their inputs and operation types are same as operation number 10 and 9 respectively. Similarly, operation number 21 and 22 are redundant in partition P3 as their inputs and operation types are same as operation number 20 and 19 respectively. These redundant operations (number 11 and 12 in partition P2 and number 21 and 22 in partition P3) are eliminated. Post applying ROE based high level transformation; the transformed DFG of ARF is shown in Fig. 11. As shown in the transformed DFG post ROE, inputs of operation 14 changes from (S5, S6) to (S3, S4) and inputs of operation 26 changes from (S9, S10) to (S7, S8). Thus elimination of operations and changes in the interconnectivity of operations incur alterations in the RTL structure in terms of change in FU resource interconnectivity and size of interconnect hardware resources such as multiplexers and demultiplexers.

## (iv) Key-driven THT based structural transformation

Tree height transformation (THT) is a high level transformation technique where height of a CDFG is subjected to alteration by breaking the sequential data dependency in the graph and forcing parallel dependency of some operations without affecting the design functionality. The alteration in the height of graph by modifying the data dependency of nodes incurs structural transformation based obfuscation in the RTL structure post HLS. The THT based high level transformation technique contributes in structural obfuscation by incurring the following modifications in the RTL datapath: modification in the interconnectivity of FU resources and size of multiplexers and demultiplexers.

The THT based structural transformation employed by (Sengupta and Rathor, 2020) is driven through designer's chosen secret SO-key4. The value of the chosen secret key determines the number of partitions that have to be subjected to the THT. The size of SO-key4 depends on the maximum number of partitions that can be subjected to the THT. The function and size of SO-key4 is highlighted in Fig. 4.

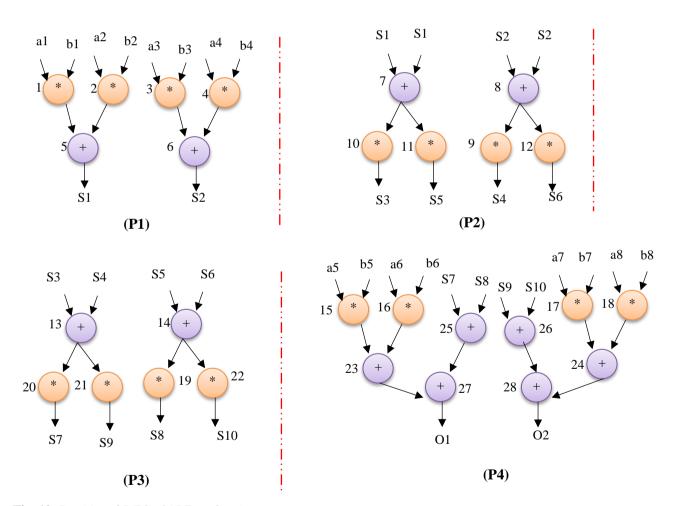

A demonstration of THT based transformation is shown using 8-point DCT application. Earlier, it has been demonstrated that how partitions of DFG of 8-point DCT are generated (shown in Fig. 8). Since ROE is not possible in the partitioned DFG of 8-point DCT, therefore it is directly subjected to THT based transformation. The THT based structural transformation is performed on the partitioned CDFG based on designer's chosen value of SO-key4. As shown in the partitioned DFG of DCT, there is maximum one partition (i.e. P2) which can be subjected to the THT. Therefore the size of SO-key4 is only 1 bit. For a designer's chosen value of SO-key4= '1', the partition P2 is subjected to the THT based structural transformation. The THT transformed partitioned DFG of DCT is shown in Fig. 12. As shown in the figure, the sequential data dependency of operation 12 in partition P2 has been converted to the parallel dependency with respect to the operation number 11. This

Fig. 12. THT based obfuscation technique on partitioned DFG of 8-point DCT

leads to alteration in the height of sub-graph in partition P2. Thus THT based structural transformation is performed to further enhance structural obfuscation in the controller design.

### (v) Key-driven folding knob based structural transformation

Post performing loop unrolling, partitioning, ROE and THT based structural transformations; all operations of the obtained obfuscated partitioned CDFG are scheduled in control steps. The folding knob based structural transformation is performed post-scheduling of the obfuscated partitioned DFG to further enhance the obscurity in the design structure. Folding is a high-level transformation technique which can be exploited to achieve structural obfuscation; such that a common resource is shared among a set of operations that have the same operation type but are present in different control steps. The number of operations in a set sharing the resource is called the 'folding factor'. Thus the folding of FU resource units depends on the secret value of chosen 'folding factor'. Further, the number of folding transformation is controlled by the designer chosen secret value of SO-key5. The value of the key5 denotes the number of folding transformations to be applied which is referred as the 'folding knob'. The maximum size of SO-key5 depends on the maximum number of occurrences of folding transformation (i.e. maximum value of folding knob) across the scheduled DFG. The folding knob based transformation affects the number of FU resources and delay elements (also known as registers) post HLS, thereby structurally obfuscating the design without causing any change to the functionality.

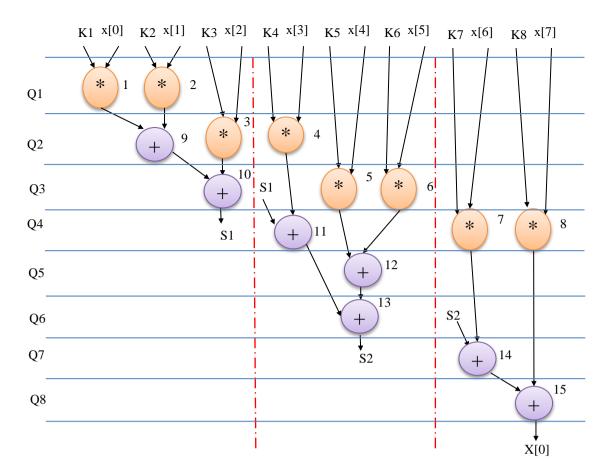

The folding knob transformation has been demonstrated using 8-point DCT core. (Sengupta and Rathor, 2020) considered folding factor =2 for applying folding-knob based transformation. So far, THT obfuscated partitions of DFG of 8-point DCT have been explained in previous step. In order to perform folding knob transformation, the THT obfuscated partitions of DFG are scheduled as shown in Fig. 13. It is evident from the figure that there are maximum 5 occurrences of folding transformation based on folding factor =2. First folding transformation can be performed in scheduled partition P1 using

Fig. 13. Scheduling of obfuscated partitioned DFG of DCT application using 2Multipliers and 1 Adder

either (operation 1 and 2) or (operation 1 and 3) because of having same operation type and different control steps. Second folding transformation can be performed in scheduled partition P1 using (operation 9 and 10). Third folding transformation can be performed in scheduled partition P2 using either (operation 4 and 5) or (operation 4 and 6). Fourth folding transformation can be performed in scheduled partition P2 using any of following set of operations: (operation 11 and 12), or (operation 11 and 13) or (operation 12 and 13). Fifth folding transformation can be performed in scheduled partition P3 using (operation 14 and 15). For designer selected value of So-key5= "011", the value of folding knob is 3 i.e. folding transformation is to be applied at three occurrences in the scheduled graph. First folding transformation is applied using operation 1 and 3 in partition P1, hence they are essentially executed through same FU resource instance (i.e. M1) as shown in Fig. 14. The second folding transformation is applied using operation 1 and 6 in partition P2, hence they are essentially executed through same FU resource instance (i.e. A1) as shown in figure. The third folding transformation is applied using operation 11 and 12 in partition P2, hence they are essentially executed through same FU resource instance (i.e. A1) as shown in figure. The operations that are subjected to folding are encircled in loops as shown in Fig. 14. The allocation of other operations to the FU resources does not comply with the folding transformation. A possible allocation of remaining

operations is shown in the Fig. 14. As shown in the figure, the obfuscated partitioned DFG of DCT application uses two multipliers and one adder for FU resource allocation.

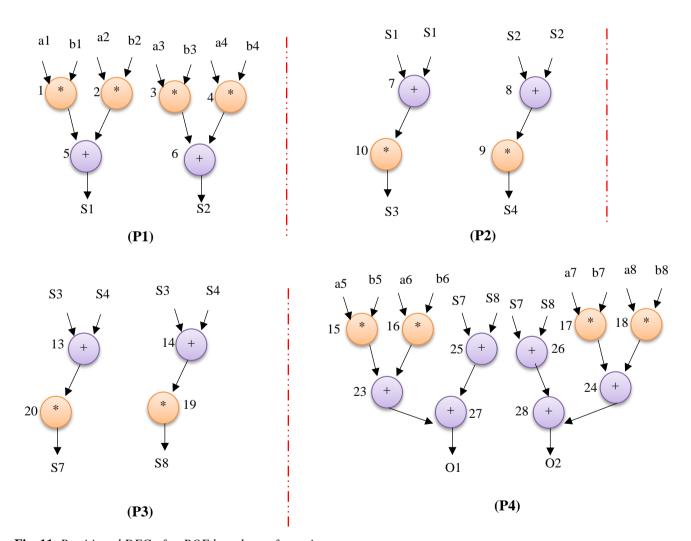

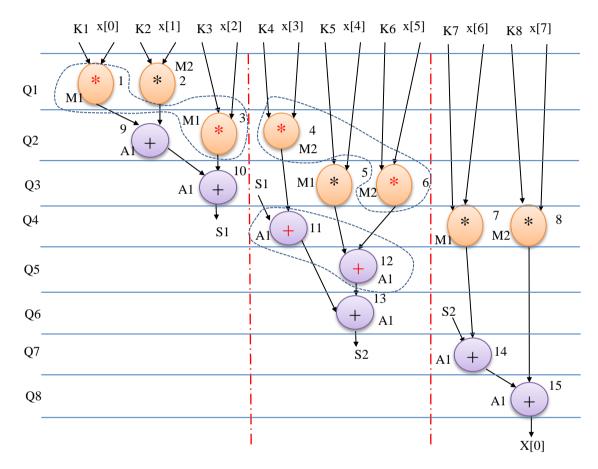

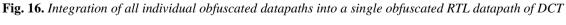

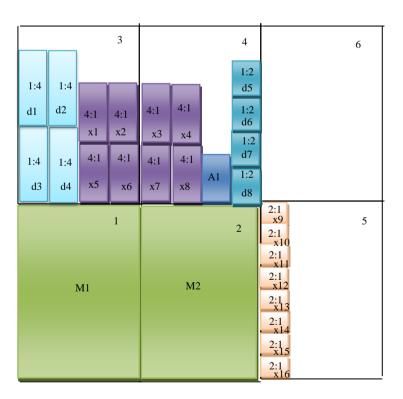

Once multiple key driven techniques of structural obfuscation are performed, the individual obfuscated scheduled partitions of the graph are synthesized into individual obfuscated RTL datapath. The individual obfuscated RTL datapath of three scheduled DFG partitions (refer Fig. 14) of 8-point DCT are shown in Fig. 15. Further, these individual obfuscated RTL datapaths are integrated into a single obfuscated RTL datapath. Fig. 16 shows the integration of individual obfuscated datapath of scheduled DFG partitions into a single obfuscated RTL datapath. This obtained structurally obfuscated RTL

Fig. 14. Folding knob based transformation on obfuscated partitioned DFG of 8-point DCT architecture is harder to reverse engineer by an adversary, hence it becomes secured against Trojan insertion and piracy

## (b) Multiple variables signature based physical level watermarking - the second line of defence

threats.

The watermarking based second line of defence is performed on the top of structurally obfuscated design. In this approach of second line of defence (Sengupta and Rathor, 2020), watermarking has been performed at physical level by embedding three variables vendor's signature. To do so, physical level design step in the form of early floorplanning has been introduced by

(Sengupta and Rathor, 2020) in the physical design flow. In the early floorplanning step of physical design flow, an early

Fig. 15. Obfuscated RTL datapath of individual scheduled DFG partitions of 8-point DCT

floorplan of RTL components is prepared which is subjected to watermarking constraints. The overall process of accomplishing physical level watermark is illustrated using following steps:

## (i) Formation of a set of RTL components

Firstly, RTL components are extracted from the structurally obfuscated datapath. A set 'R' of RTL components such as FUs (adders, multipliers, subtractors and comparator etc.), interconnect hardware resources (multiplexers and demultiplexers of various sizes) is formed. The different type of RTL components in the set 'R' are arranged in the decreasing order of their size; and, different instances of the same RTL component are arranged in the set in increasing order of their instance number. For example, a set of RTL components obtained from obfuscated RTL datapath of 8-point DCT (shown in Fig. 16) is given below:

R= {M1, M2, d1, d2, d3, d4, x1, x2, x3, x4, x5, x6, x7, x8, A1, d5, d6, d7, d8, x9, 10, x11, x12, x13, x14, x15, x16} (2)

The RTL components shown in the set 'R' have been ordered based on their size and instance number. Note: these components have been highlighted using red colour in the integrated obfuscated RTL datapath shown in Fig. 16.

Thus a set of RTL components is formed, which is used in the further steps of embedding physical level watermarking.

#### (ii) Preparing early floorplan

Once a set of RTL components is formed, it is utilized in preparing early floorplan. To prepare the early floorplan, the elements (i.e. RTL components) in the set 'R' are traversed from left to right. While traversing the set, each component of

## RTL components of datapath of scheduled partition P1

| FU       | Associated interconnect  |

|----------|--------------------------|

| resource | resources                |

| M1       | 2:1 Mux1_M1, 2:1 Mux2_M1 |

|          | 1:2 Demux1_M1            |

| M2       |                          |

| A1       | 2:1 Mux1_A1, 2:1 Mux2_A1 |

|          | 1:2 Demux1_A1            |

## RTL components of datapath of scheduled partition P2

| FU       | Associated interconnect  |

|----------|--------------------------|

| resource | resources                |

| M1       |                          |

| M2       | 2:1 Mux1_M2, 2:1 Mux2_M2 |

|          | 1:2 Demux1_M2            |

| A1       | 4:1 Mux1_A1, 4:1 Mux2_A1 |

|          | 1:4 Demux1_A1            |

# RTL components of datapath of scheduled partition P3

| FU       | Associated interconnect  |

|----------|--------------------------|

| resource | resources                |

| M1       |                          |

| M2       |                          |

| A1       | 2:1 Mux3_A1, 2:1 Mux4_A1 |

|          | 1:2 Demux2_A1            |

## RTL components of integrated datapath

| FU       | Associated interconnect resources    |

|----------|--------------------------------------|

| resource |                                      |

| M1       | 4:1 Mux1_M1 (x1), 4:1 Mux2_M1 (x2)   |

|          | 1:4 Demux1_M1 ( <mark>d1</mark> )    |

|          | 2:1 Mux1_M1 (x9), 2:1 Mux2_M1 (x10)  |

|          | 1:2 Demux1_M1 (d5)                   |

| M2       | 4:1 Mux1_M2 (x3), 4:1 Mux2_M2 (x4)   |

|          | 1:4 Demux1_M2 ( <mark>d2)</mark>     |

|          | 2:1 Mux1_M2 (x11), 2:1 Mux2_M2 (x12) |

|          | 1:2 Demux1_M2 (d6)                   |

| A1       | 4:1 Mux1_A1 (x5), 4:1 Mux2_A1 (x6)   |

|          | 1:4 Demux1_A1 (d3)                   |

|          | 4:1 Mux3_A1 (x7), 4:1 Mux4_A1 (x8)   |

|          | 1:4 Demux2_A1 ( <mark>d4)</mark>     |

|          | 2:1 Mux1_A1 (x13), 2:1 Mux2_A1 (x14) |

|          | 1:2 Demux1_A1 ( <mark>d7)</mark>     |

|          | 2:1 Mux3_A1 (x15), 2:1 Mux4_A1 (x16) |

|          | 1:2 Demux2_A1 ( <mark>d8)</mark>     |

| I        |                                      |

**Note**: 'x' and 'd' represent multiplexers and demultiplexers respectively. Numbering of components has been done in decreasing order of their size and increasing order of instance number

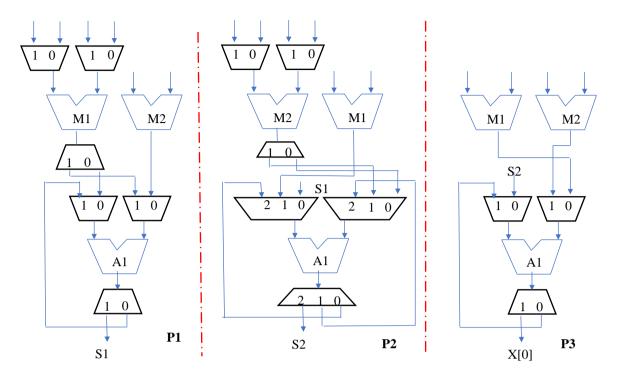

different type is selected according to their order of presence (in the set 'R') and placed in the floorplan in order to make it grow diagonally i.e. 'd' appears before 'x'. *Note: however selection within components of same size can be made randomly*. To facilitate the growth of floorplan, it is partitioned into equal sized blocks. The size of each block is given by the following:

Block size = (largest component height in the set 'R') \* (largest component width in the set 'R') (3)

For the set of components of obfuscated RTL datapath of 8-point DCT core, the largest component height is of multiplier and the largest component width is also of multiplier. For the height=8 units and the width= 4 units of multiplier, the size of each block is 8×4.

Once first block is filled post placement of RTL components, further placement of components is performed in the second block which is placed just right to the first block in the floorplan. Further the third block is placed on the top of the first block in order to make diagonal growth of floorplan and maintain a rectangular envelop. Thus early floorplan is prepared using RTL components as shown in Fig. 17. The second line of defence in the form of physical level watermarking is performed on this generated early floorplan of the obfuscated design.

#### (iii) Selection of vendors signature and conversion into watermarking constraints

In order to embed vendor's watermark into the early floorplan, a secret signature comprising of three unique variables  $\alpha$ ,  $\beta$  and  $\gamma$  is selected. To enable embedding of signature into the floorplan, the mapping of signature variables into watermarking constraints is shown in Table 1. Based on these mapping rules, each digit of the signature is decoded and embedded into the

Fig. 17. Early floorplan of obfuscated DCT design before embedding watermark

floorplan one by one.

For embedding watermark into the floorplan of the obfuscated DCT design, let's assume the vendor's secret signature is: " $\alpha \alpha \beta \beta \gamma \beta \gamma \beta$ ".

### (iv) Embedding of α digits into floorplan

As evident from the mapping rule of  $\alpha$  variable given in the Table 1, the embedding of  $\alpha$  digits of the signature is performed using FU resource components only. Therefore in order to embed  $\alpha$  digits, firstly a subset 'R1' containing only FU components (multipliers, adders etc.) is extracted from the set 'R', where arrangement of FU resources follow the decreasing order of size and the increasing order of instance number. Further, the elements in subset 'R1' are traversed using two pointers 'p' and 'q' in order to embed each  $\alpha$  digit. Initially, pointer 'p' indexes the 1st FU component in the subset 'R1' and pointer 'q' indexes the 2nd FU component. For each  $\alpha$  digit, pth FU component is swapped with the qth component in the subset 'R1'. If swapping leads to placement of an odd FU component on the top of the even FU component in the floorplan, then one  $\alpha$  digit is successfully embedded. Now, those FU components which participated in the embedding of  $\alpha$  digit are eliminated from the subset 'R1'. However if the swapping does not place an odd FU component on the top of the even FU component (i.e. embedding of  $\alpha$  digit is not possible) then the swapping is undone (previous placement of components in the floorplan is restored). Further, the pointer 'q' is subjected to increment by one. Again pth FU component is swapped with qth component for embedding of the  $\alpha$  digit. For each swapping, 'q' is subjected to increment by one until it reaches to its maximum value (m) which is represented by the total number of FU components of same type in the subset 'R1'. When the maximum value is reached by pointer 'q', the pointer 'p' is incremented by one and pointer 'q' is set to 'p+1'. The pointer 'p'

Table 1. Mapping of signature variables into watermarking constraints

| Variables in author's signature | Mapping rules to map into watermarking constraints                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| α                               | Odd FU resource needs to be placed on the top of even FU by swapping between two FU resources of same type                           |

| β                               | Odd multiplexer (Mux) needs to be placed on the top of even multiplexer by swapping between two multiplexers of same size            |

| γ                               | Odd demultiplexers (Demux) needs to be placed to the right of even demultiplexer by swapping between two demultiplexers of same size |

can go upto m-1. When the traversal of all components of a particular FU type is accomplished, pointers 'p' and 'q' are made to index the first two components of another FU type in the subset 'R1'. This process is followed until the embedding of all  $\alpha$  digits in the signature is accomplished.

In case of 8-point DCT design, the subset R1 extracted from set R is as follows:

$$R1 = \{M1, M2, A1\}$$

(4)

For embedding first  $\alpha$  digit of the signature, the subset R1 is traversed to perform swapping between components of same size. Initially, components M1 and M2 are indexed by pointers 'p' and 'q' respectively. Therefore, components M1 and M2 are subjected to swapping. However, this swapping does not place an odd FU component on the top of even FU component (according to the embedding rule of  $\alpha$  variable). Therefore this swapping is undone. Further swapping of components by increasing the pointer 'q' and/or 'p' in the subset 'R1' is not possible because of very limited number of FU components in the subset. Therefore embedding of any  $\alpha$  digit is not possible in the floorplan of obfuscated 8-point DCT design.

#### (v) Embedding of β digits into floorplan

As evident from the mapping rule of  $\beta$  variable given in the Table 1, the embedding of  $\beta$  digits of the signature is performed using Mux components only. Therefore in order to embed  $\beta$  digits, firstly a subset R2 containing only Mux components of different sizes is extracted from the set 'R', where arrangement of Mux components follow the decreasing order of size and the increasing order of instance number. Likewise the embedding process of  $\alpha$  digits, the elements in subset 'R2' are traversed using two pointers 'p' and 'q' in order to embed each  $\beta$  digit of the signature. Initially, pointer 'p' and 'q' index the 1<sup>st</sup> and 2<sup>nd</sup> Mux component of same size. For each  $\beta$  digit, p<sup>th</sup> Mux component is swapped with the q<sup>th</sup> Mux component of the same size in the subset 'R2'. If swapping leads to placement of an odd Mux component on the top of the even Mux component in the floorplan, then one  $\beta$  digit is successfully embedded. Now, those Mux components which participated in the embedding of  $\beta$  digit are eliminated from the subset 'R2'. However if the swapping does not make embedding of  $\beta$  digit possible, then the swapping is undone. During the embedding of  $\beta$  digits, the pointers 'p' and 'q' are incremented in the same manner as was discussed for embedding of  $\alpha$  digits.

The embedding of  $\beta$  digits is demonstrated using early floorplan (shown in Fig. 17) of obfuscated DCT design. In order to do so, the subset R2 is extracted from set R which is given as follows:

$$R2 = \{ x1, x2, x3, x4, x5, x6, x7, x8, x9, 10, x11, x12, x13, x14, x15, x16 \}$$

(5)

To embed  $1^{st}$   $\beta$  digit of the signature, the subset R2 containing all Mux components is traversed and swapping is performed between components of same size. Initially, Mux components x1(4:1) and x2(4:1) are indexed by pointers 'p' and 'q' respectively, hence subjected to swapping for embedding  $1^{st}$   $\beta$  digit. The **swapping of x1 and x2** will result into embedding

of first  $\beta$  digit (as per the embedding/mapping rule of ' $\beta$ '). This is because, it will place x1 (odd component) over x6 (even component). Since the embedding of 1<sup>st</sup> β digit has utilized Muxes x1 and x6, therefore they are removed from the subset R2. The modified subset R2 is as follows:  $R2 = \{x2, x3, x4, x5, x7, x8, x9, 10, x11, x12, x13, x14, x15, x16\}$ . Now for embedding next β digit, pointers 'p' and 'q' are made to index again first two components i.e. x2(4:1) and x3(4:1) respectively in the subset 'R2'. Now swapping of x2 and x3 in the floorplan is performed which will not result into embedding of second β digit. This is because the swapping will cause the placement of x2 (even) on the top of x7 (odd) and x3 (odd) on the top of x5 (odd). Here, neither of the cases follows the embedding/mapping rule of 'β'. Therefore this swapping is undone. Now pointer 'q' is incremented by one and it starts indexing x4 in the subset 'R2'. Further, swapping of x2 and x4 in the floorplan is performed which also will not result into embedding of second  $\beta$  digit. This is because the swapping will cause the placement of x2 (even) on the top of x8 (even) and x4 (even) on the top of x5 (odd). Here again, neither of the cases follows the embedding/mapping rule of 'β'. Therefore this swapping is also undone. Now pointer 'q' is again incremented by one and it indexes x5 in the subset R2. Now swapping of x2 and x5 will result into embedding of second β digit (as per the embedding/mapping rule of '\beta'). This is because, it will place x5 (odd component) over x2 (even component). Since the embedding of the β digit has utilized Muxes x2 and x5, therefore they are also removed from the subset R2. The modified subset R2 is as follows:  $R2 = \{x3, x4, x7, x8, x9, 10, x11, x12, x13, x14, x15, x16\}$ . Now for embedding next  $\beta$  digit, pointers 'p' and 'q' are made to index again first two components i.e. x3(4:1) and x4(4:1) respectively in the subset 'R2'. Swapping

**Fig. 18.** *Intermediate watermarked floorplan post embedding*  $\beta$  *digits of the signature*

of x3 and x4 will result into embedding of third  $\beta$  digit. This is because, it will place x3 (odd component) over x8 (even component). Since the embedding of the  $\beta$  digit has utilized Muxes x3 and x8, therefore they are also removed from the subset 'R2'. The modified subset 'R2' is as follows: R2= { x4, x7, x9, 10, x11, x12, x13, x14, x15, x16}. Further, swapping of x4 and x7 will result into embedding of 4<sup>th</sup>  $\beta$  digit. This is because, it will place x7 (odd component) over x4 (even component). This is how all four  $\beta$  digits of the signature are embedded in to the floorplan. The intermediate floorplan post embedding all  $\beta$  digits is shown in Fig. 18. As shown in the figure, the embedded  $\beta$  digits (i.e. odd Muxes on the top of even Muxes) have been highlighted using red colour.

## (vi) Embedding of $\gamma$ digits into floorplan

As evident from the mapping rule of  $\gamma$  variable given in the Table 1, the embedding of  $\gamma$  digits of the signature is performed using Demux components only. Therefore in order to embed  $\gamma$  digits, firstly a subset R3 containing only Demux components of different sizes is extracted from the set 'R', where arrangement of Demux components follow the decreasing order of size and the increasing order of instance number. Likewise the embedding rule of  $\alpha$  digits, the elements in subset 'R3' are traversed using two pointers 'p' and 'q' in order to embed each  $\gamma$  digit of the signature. Initially, pointers 'p' and 'q' index the 1<sup>st</sup> and 2<sup>nd</sup> Demux component of same size. For each  $\gamma$  digit, p<sup>th</sup> Demux component is swapped with the q<sup>th</sup> component of same size in the subset 'R3'. If swapping leads to placement of an odd Demux component to the right of an even Demux component in the floorplan, then one  $\gamma$  digit is successfully embedded. Now, those Demux components which participated in the embedding of  $\gamma$  digit are removed from the subset 'R3'. However if the swapping does not make embedding of  $\gamma$  digit possible, then the swapping is undone. During the embedding of  $\gamma$  digits, the pointers 'p' and 'q' are incremented in the same manner as was discussed for embedding of  $\alpha$  and  $\beta$  digits.

The embedding of  $\gamma$  digits in the floorplan of the obfuscated DCT design is discussed as follows. Firstly, the subset R3 is extracted from set R as given below.

$$R3 = \{d1, d2, d3, d4, d5, d6, d7, d8\}$$

(6)

To embed 1<sup>st</sup>  $\gamma$  digit of the signature, the subset 'R3' containing all Demux components is traversed and swapping is performed between components of same size. Initially, Demux components d1(1:4) and d2(1:4) are indexed by pointers 'p' and 'q' respectively, hence subjected to swapping for embedding 1<sup>st</sup>  $\gamma$  digit. The swapping of d1 and d2 will result into embedding of first  $\gamma$  digit (as per the embedding/mapping rule of ' $\gamma$ '). This is because, it will place d1 (odd component) right to the d2 (even component). Since the embedding of 1<sup>st</sup>  $\gamma$  digit has utilized Demuxes d1 and d2, therefore they are removed from the subset 'R3'. The modified subset 'R3' is as follows: R3= {d3, d4, d5, d6, d7, d8}. Now for embedding next  $\gamma$  digit, pointers 'p' and 'q' are made to index again first two components i.e. d3(1:4) and x4(1:4) respectively in the subset 'R3'.

**Fig. 19**. Final watermarked floorplan post embedding  $\beta$  and  $\gamma$  digits of the signature

Now swapping of d3 and d4 in the floorplan is performed which will also result into embedding of  $\gamma$  digit. This is because, it will place d3 (odd component) right to the d4 (even component). This is how both  $\gamma$  digits of the signature are embedded in to the floorplan. The floorplan post embedding all  $\gamma$  digits is shown in Fig. 19. As shown in the figure, the embedded  $\gamma$  digits (i.e. odd Demuxes at the right to the even Demuxes) have been highlighted using Red colour. The floorplan in Fig. 19 is the final watermark embedded floorplan of the obfuscated RTL design of DCT core.

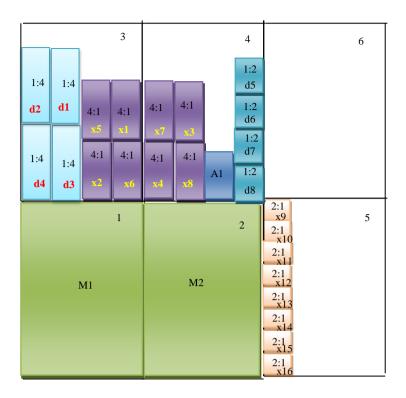

### (c) Detection of Watermark

Detection of watermark into a design under-test proves the authenticity of the design. Absence of vendor's watermark into a design of the brand of a genuine vendor indicates that probably an adversary is misusing the brand of the genuine vendor to illegally sell counterfeited designs into the market. Hence, detection of the absence of watermark identifies the counterfeiting. Only those designs of vendor's brand would be proved authentic which contain the watermark (vendor's signature) of genuine owner. The detection of author's signature to identify his/her watermark is performed in following steps as shown in Fig. 20:

#### (i) Watermark constraints re-generation for verification

In this step, the watermarking constraints are regenerated from the vendor's signature comprising of  $\alpha$ ,  $\beta$  and  $\gamma$  variables. The re-generation of watermarking constraints is performed by applying vendor's /designer's specified mapping rules to the signature digits. Further, the presence of re-generated watermarking constraints is verified into the design.

#### (ii) Inspection of watermark into the design

Fig. 20. Detection of signature digits embedded during physical level watermarking (Sengupta and Rathor, 2020)

The final floorplanned design file obtained from the physical design tool is subjected to watermark detection. The following inputs are required to generate the final floorplanned design file during physical design process: (a) Verilog file of the DSP core design netlist (b) configuration file (c) watermarked early floorplan file of obfuscated design (this file contains the vendor's signature which represents the watermark) (e) library files (f) any other relevant files. In the floorplanned design file, orientations of RTL components are inspected to detect the watermark.

### (iii) Verification of watermark constraints (signature digits)

If orientation of RTL components in the floorplanned design file is according to the watermark constraints (obtained post mapping of signature digits in first step), then the presence of original vendor's (author's) signature is verified in the design. Detection of author's signature (representing watermark) in the design of the brand of genuine author proves that the design is authentic. However, if the author's signature is missing in the design of the brand of genuine author, then probably those designs are counterfeited/ not authentic.

## 3. Key Size Analysis of the Structural Obfuscation

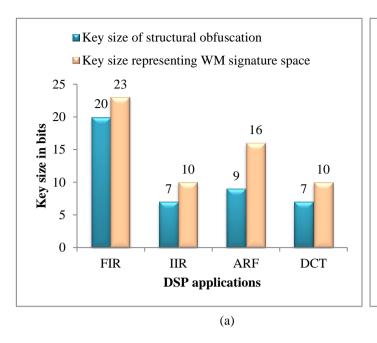

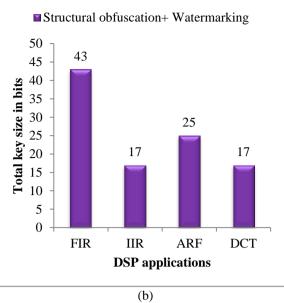

The total SO-key size (KS<sub>total</sub>) of multi-structural transformation based obfuscation process is calculated as follows:

$$KS_{total} = \{ [(\log_2(U_m))] + [(\log_2(C_m))] + [(\log_2(R_m))] + [(\log_2(T_m))] + [(\log_2(F_m))] \}$$

bits (7)

Where,  $U_m$  indicates maximum value of UF,  $C_m$  indicates maximum cuts possible,  $R_m$  indicates maximum ROs possible,  $T_m$  indicates maximum THT possible and  $F_m$  indicates maximum folding possible. Driving the multiple techniques of structural transformations viz. loop unrolling, partitioning, ROE, THT and folding knob through individual SO-keys enhances the security level against RE (which results into Trojan insertion and piracy). Because of the involvement of multi-layered secret SO-keys in the structural transformations based obfuscation, the difficulty level of deducing true functionality and structure through RE by an attacker is augmented. This is because; now an attacker has to know both the multiple secret SO-keys and the structural transformation techniques to back-engineer the original functionality and structure. Further, finding true key combination among the exhaustive key combinations is difficult for the attacker. Hence, de-obfuscation becomes arduous for an attacker as the secret SO-keys, which are used to perform high level transformation based obfuscation, are not known to the attacker.

## 4.6. Low-cost Optimized Multi-key based Structural Obfuscation

This section presents a discussion on why a low cost and optimized version of multi-key based structural obfuscation is useful and how it is achieved. The discussion has been divided in following sub-sections:

## 1. Motivation for Low-Cost Optimized Structural Objuscation

Selection of an optimal (resulting into low-cost) design from a vast number of functionally equivalent architecture designs requires extensive analysis of the design space. Exploring low-cost solution using design space exploration (DSE) framework, while simultaneously performing multiple structural transformations driven obfuscation based security is vital in two ways: (i) it minimizes the overhead impact caused due to employing structural obfuscation based security (ii) it ensures that the designer's area, power and delay budget is satisfied. This motivates the integration of DSE framework with the multiple high level transformations driven structural obfuscation based security technique. This section discusses how the particle swarm optimization (PSO) process (Mishra and Sengupta, 2014) is exploited to explore the design space in order to yield a low-cost obfuscated design without hampering the functionality of the DSP core. Below some approaches are mentioned where even though obfuscation has been used for security, however exploration of low cost solution has not been addressed.

A brief discussion on some approaches that secures DSP cores using obfuscation technique is as follows: Approaches proposed by (Chakraborty, Bhunia, 2009; Chakraborty, Bhunia, 2011) applied obfuscation based IP core security against Trojan insertion attacks. However, high level synthesis (HLS) framework has not been leveraged by these approaches to perform obfuscation. Further these approaches (Chakraborty, Bhunia, 2009; Chakraborty, Bhunia, 2011) do not target DSP cores and do not explore

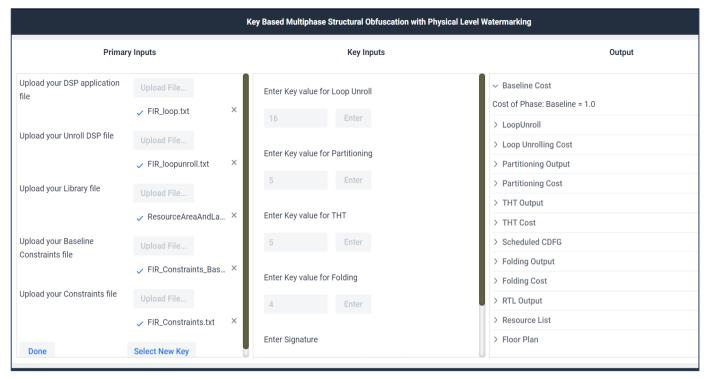

Fig. 21. Overview of low-cost key-based structural obfuscation approach

low-cost solution. In approaches proposed by (Lao and Parhi, 2015; Sengupta and Roy, 2017) structural obfuscation has been applied on DSP cores. However, these approaches do not explore the design space to ensure the low design cost. Therefore, this section presents a discussion on how the PSO-DSE is integrated with the key-based transformation driven structural obfuscation for DSP cores to explore a low-cost obfuscated design.

#### 2. High Level Perspective

High level view of the methodology of generating low-cost obfuscated designs is shown in Fig. 21. It comprises of three major modules viz. key driven structural obfuscation module, PSO module and fitness/cost evaluation module. The structural obfuscation module employed in this approach accepts a CDFG (of the corresponding DSP application) and secret keys as inputs and produces a structurally modified but functionally equivalent CDFG design as output. The output of the structural obfuscation module serves as the input to the PSO-DSE module which determines the optimal resource configuration that would incur minimal design cost. PSO-DSE process uses the fitness/cost evaluation module for computing cost and finally a low-cost highly secured structurally obfuscated design is generated.

### 3. Details of Methodology

Figure 22 shows detailed description of the low-cost multi-key based structural obfuscation approach. The inputs are a CDFG representing a DSP application, module library, PSO control parameters (iteration count, swarm size, acceleration coefficient etc.) and secret multi-key values for obfuscation as shown in the figure. The first transformation i.e. key-based loop unrolling is applied to the input CDFG depending on its applicability; thereafter the CDFG is partitioned into as many partitions as per the specification of the designer's secret key. Further, redundant nodes elimination process is performed from the CDFG based on the designer's secret key, and then finally key-based tree height transformation is applied to the CDFG. Subsequently, PSO-DSE is applied to determine optimal resource constraints that would yield minimal design cost. Based on the optimal resource constraints, final scheduling is performed on the CDFG. The final obfuscation technique i.e. folding is performed on scheduled CDFG which results into structurally obfuscated scheduled CDFG of DSP core. Further upon performing datapath and controller

generation of HLS, structurally obfuscated register transfer level (RTL) design is generated.

## (a) Summary of key-driven structural transformation based obfuscation and their effect on gate count/design cost

- (i) Loop Unrolling (Sengupta and Rathor, 2020): It is a high-level transformation technique used to obfuscate the loop-based DSP core by untwining the loop based on the secret SO-key1. The loop unrolling affects number of control steps in the controller and increases logic density, thereby causing a change in the gate count (and structure) without changing functionality.

- (ii) Partitioning (Sengupta and Rathor, 2020): This high-level transformation technique is performed to obfuscate the CDFG by dividing it into a number of partitions depending on the secret SO-key2. Partitioning affects the count of multiplexers and demultiplexers in the final RTL, thereby changing the gate count (and structure) without causing any change to the functionality of the CDFG.

- (iii) Redundant Operation Elimination (Sengupta and Rathor, 2020): This high-level transformation technique is performed to obfuscate the CDFG by removing redundant nodes from the graph based on the secret SO-key3. Elimination of redundant nodes affects the logic density thereby decreasing cost and also decreasing the gate count (and structure) without causing any change to the functionality.

- (iv) Tree Height Transformation (Sengupta and Rathor, 2020): This high-level transformation technique is performed to obfuscate the CDFG by transforming the height of partitioned graph based on secret SO-key4. It leads to a decrease in the number of control steps, thereby decreasing gate complexity as well as count of the controller design and design cost.

- (v) Folding (Sengupta and Rathor, 2020): It is a high-level transformation technique in which a common resource is shared among a set of nodes that have the same operation type but are present in successive control steps in the scheduled graph. The value of the secret SO-key5 specified by the user denotes the number of folding transformations to be applied which is referred as the folding knob. Sharing of resources enables maximum utilization of resources, thereby decreasing the cost.

## (b) PSO-DSE based framework for generating low-cost design solution

A generic PSO has been mapped to DSE process in high level synthesis (HLS) framework and is integrated with key based structural obfuscation to generate low cost structurally obfuscated DSP design. The PSO-DSE process comprises of five steps namely (i) particle initialization (ii) velocity computation (iii) position computation (iv) fitness evaluation and (v) finding global and local best positions. Steps (ii)-(v) are repeated for each particle over the iterations, until either terminating criterion is met (e.g. 100 iterations are completed) or there is no change in the global best position for some successive iterations (e.g. 10). The

detailed explanation of each step is given below (Mishra and Sengupta, 2014).

- (i) Particle Initialization: Dimension of particle position equals number of types of resources (for example in this approach, it is a 4-D vector because there are four types of resources for the case studies tested viz. adder, subtractor, multiplier and comparator). Position of first particle from the population is initialized with maximum resource constraints i.e.  $R_{max}$ . Position of second particle is initialized with minimum resource constraints i.e.  $R_{min}$ . Position of the third particle is initialized to average of the positions of the first two particles i.e.  $(R_{max}+R_{min})/2$ . Then the position of the remaining particles is initialized with random values between minimum resource constraints and maximum resource constraints.

- (ii) Velocity Computation: Velocity of a particle is computed using following equation (Mishra and Sengupta, 2014):

$$V_{new} = \omega * V_{old} + b_1 * r_1 * (R_{lb} - R_{curr}) + b_2 * r_2 * (R_{gb} - R_{curr})$$

(8)

where  $\omega$  is inertia weight which linearly decreases from 0.9 to 0.4 (to obtain global best),  $b_1$  and  $b_2$  are acceleration coefficients.  $b_1$  linearly decreases from 3 to 2,  $b_2$  linearly increases from 2 to 3 over the iterations of PSO. Further,  $r_1$  and  $r_2$  are random values between 0 and 1,  $R_{curr}$ ,  $R_{lb}$  are the current and best position of the current particle and  $R_{gb}$  is the best position considering all the particles so far. Initial velocity for every particle is assigned to zero. Velocity computation is followed by velocity clamping using the following (Mishra and Sengupta, 2014):

$$V_{new}^{i} = \begin{cases} V_{max}^{i}, & \text{if } V_{new}^{i} > V_{max}^{i} \\ -V_{max}^{i}, & \text{if } V_{new}^{i} < -V_{max}^{i} \\ V_{new}^{i}, & \text{otherwise} \end{cases}$$

(9)

Where  $V^i$  means velocity of i<sup>th</sup> dimension, and  $V^i_{max}$  is given by  $(R^i_{max}-R^i_{min})/2$ .

(iii) *Position Computation*: Position is computed by moving in the direction of velocity. Position is calculated using the following (Mishra and Sengupta, 2014):

$$R_{\text{new}} = R_{\text{old}} + V_{\text{new}} \qquad (10)$$

If the new position calculated exceeds maximum resource constraints then clamping is applied by selecting a random value between minimum and maximum resource constraints for each dimension.

(iv) *Fitness Evaluation:* Fitness value for each particle in the population is computed using the following cost function (Mishra and Sengupta, 2014):

$$Cost = w_1 * \left(\frac{A}{A_{max}}\right) + w_2 * \left(\frac{L}{L_{max}}\right)$$

(11)

Where, A and L are area and latency of the design with constrains of the particle and  $A_{max}$ ,  $L_{max}$  are maximum possible area and latency. Further,  $w_1$  and  $w_2$  are the designer specified weights (each taken as 0.5).

Fig. 22. Details of low-cost key-based structural obfuscation approach

- (v) Determining Local and Global Best: Local best is the best position (i.e. the position at which the cost value for the particle is minimum) achieved by a particle so far. Global best is the position at which the cost value is minimum for the entire population (i.e. minimum cost of all the local bests).

- (vi) *Mutation:* Mutation is applied in order to avoid getting stuck in local minima. It is applied on every fifth iteration with designer's choice of probability of mutation. And, it is applied on local best position of every particle. Further, mutation is applied by performing a left shift operation on every particle with even index, followed by position clamping. On every particle with odd index, mutation is applied by adding a random value (between minimum and maximum resource constraints) to the values at even index of the particle position vector and subtracting the same value from the values at odd index of the particle position vector, followed by position clamping. Then fitness/cost is evaluated at this new position obtained after mutation. If the cost value is lesser than value computed using the local best, then the local best is updated with the new position.

Thus low-cost structurally obfuscated design is generated post-performing PSO-DSE.

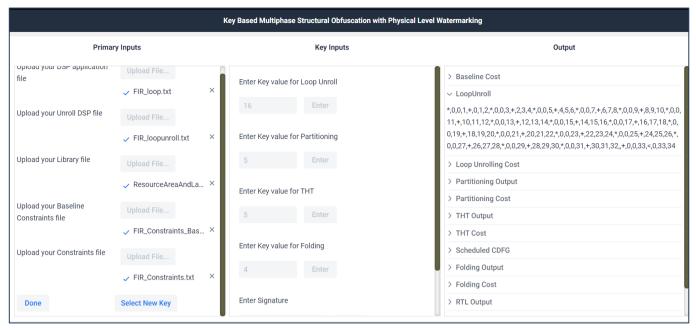

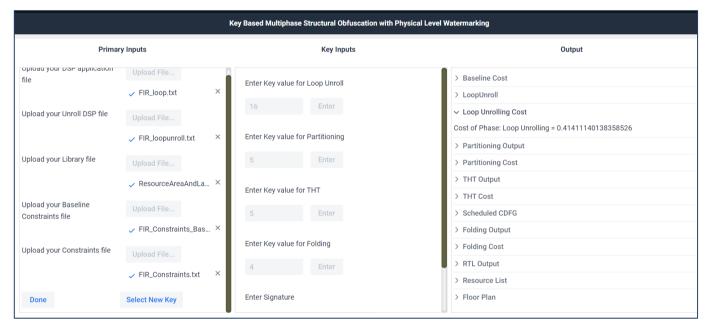

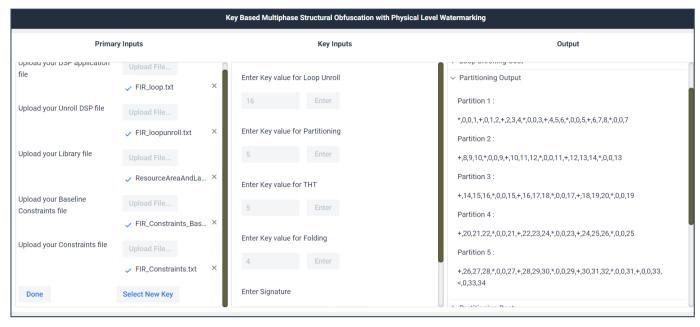

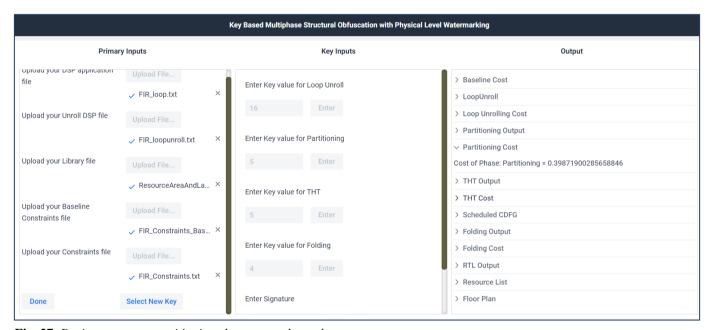

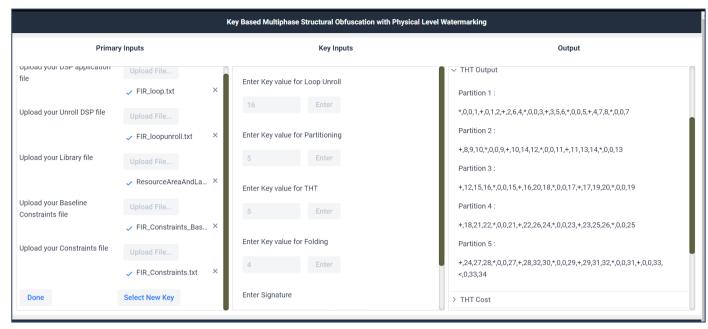

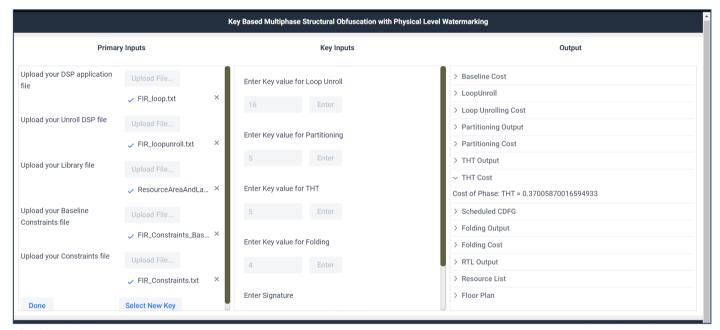

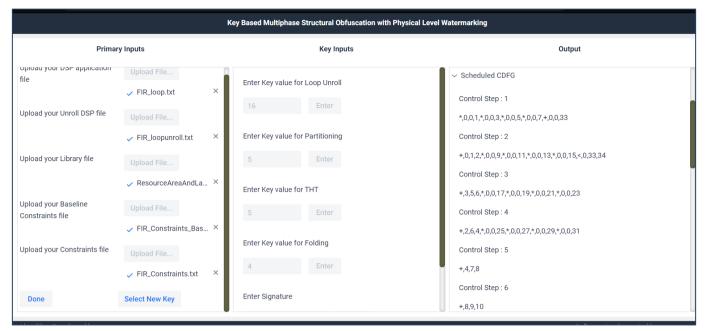

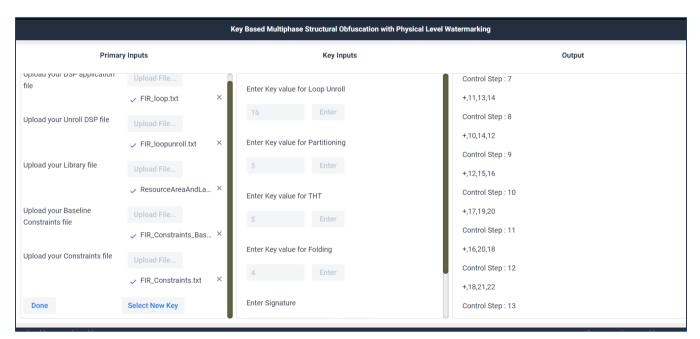

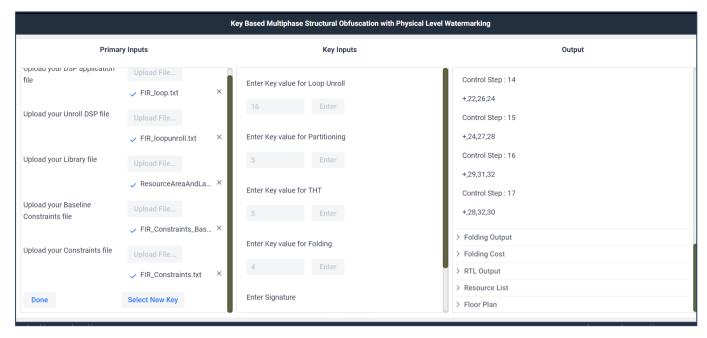

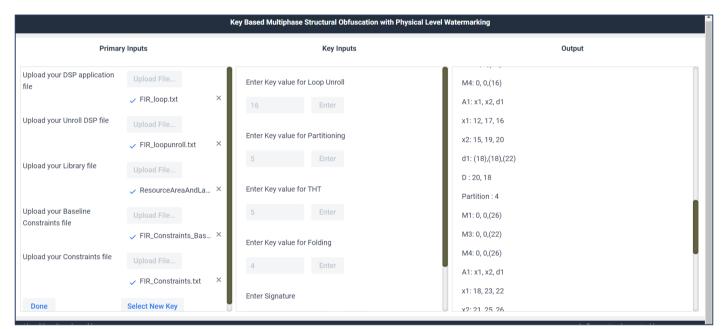

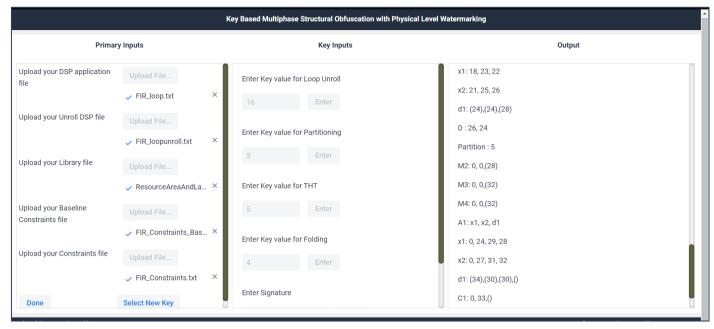

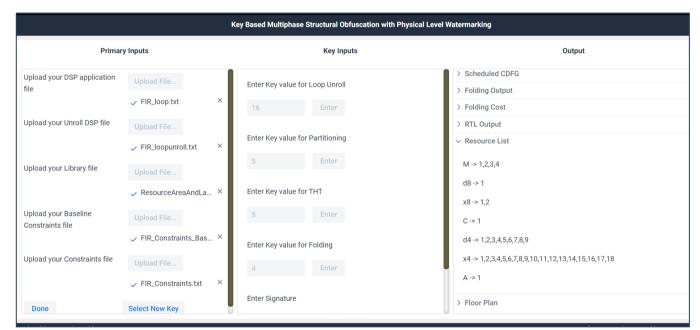

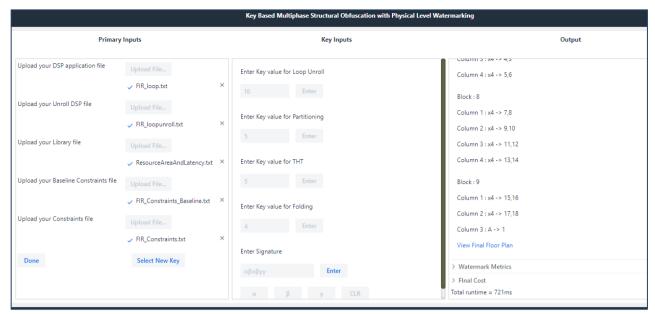

## 4.7. Structural Obfuscation and Physical level Watermarking Tool for Securing Hardware Accelerators

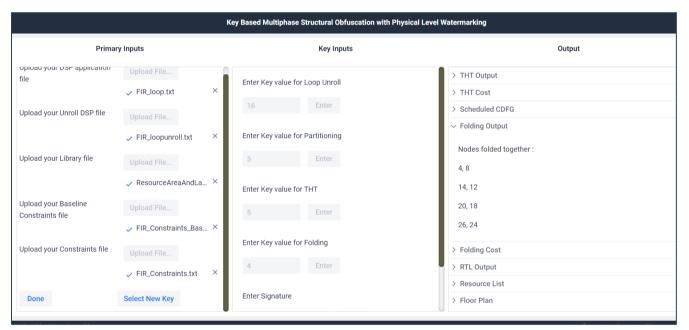

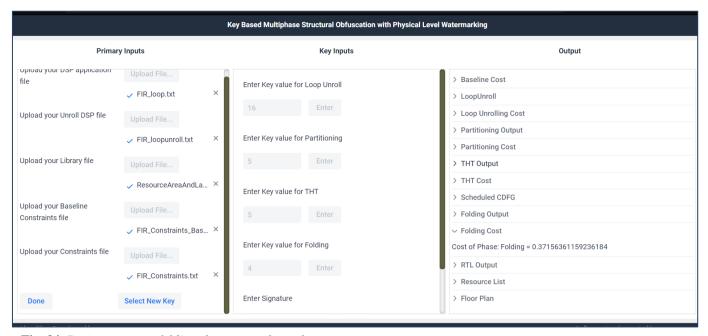

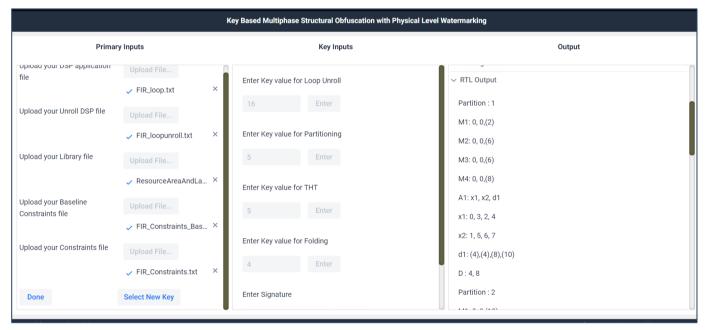

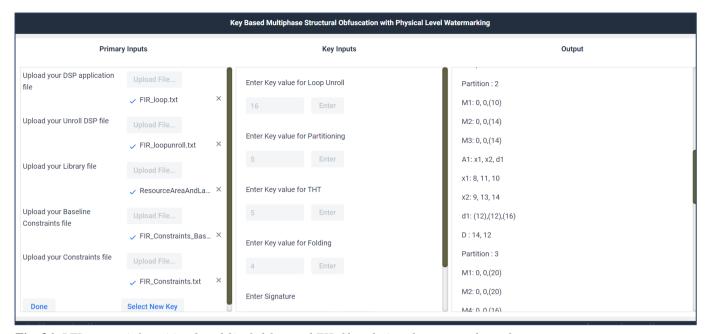

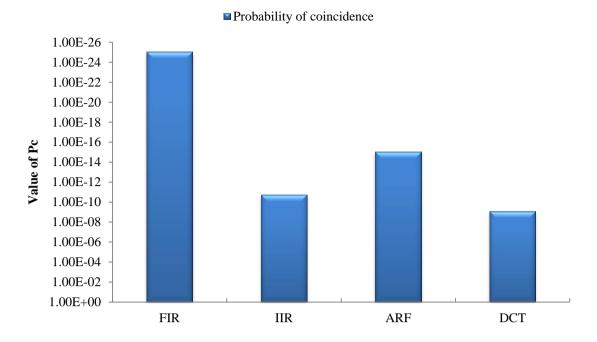

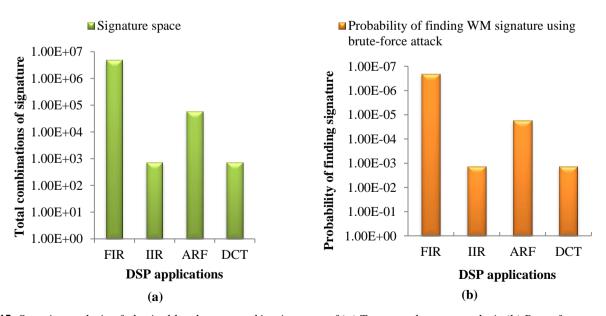

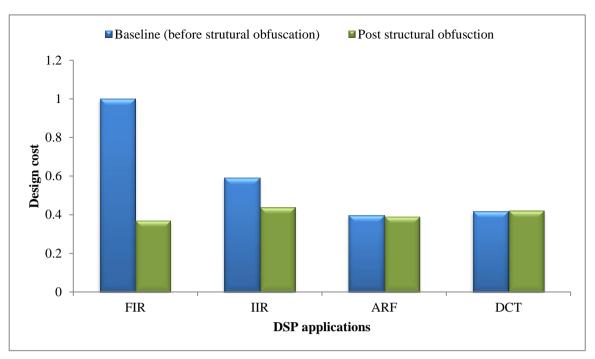

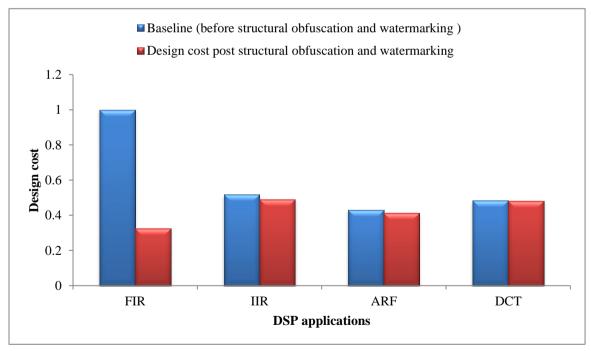

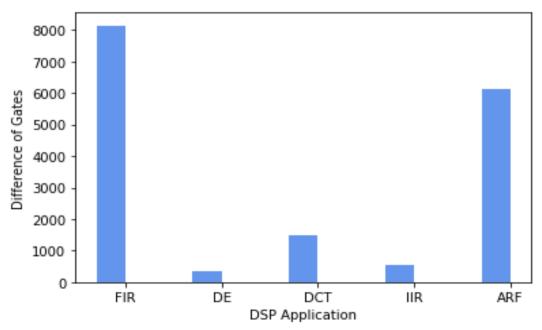

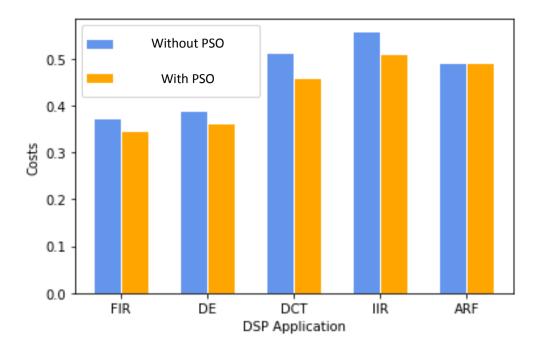

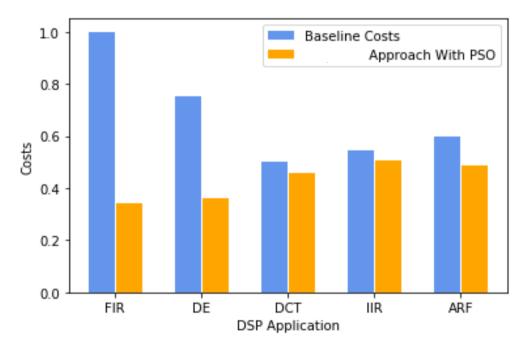

Fig. 23. A snapshot of GUI of KSO-PW tool